10GBASE-KR Ethernet TRD

60

UG1058 (v2017.1) April 19, 2017

Chapter 4:

Implementing and Simulating the Design

Simulating the Design

The 10GBASE-KR TRD can be simulated using the Vivado Design Suite simulator. The TRD

can also be simulated using Modelsim/Questa. Refer to

Vivado Design Suite User Guide:

Logic Simulation

(UG900)

, for information describing how to run simulations with

different simulators.

The simulation environment sets up the Traffic Generator and Monitor blocks of the TRD.

The Traffic Generator for channel 0 generates 10 packets which are transmitted to the

10-Gigabit Ethernet MAC IP core. The packets are looped back on the PHY and become

receive packets on channel 1. Similarly, the Traffic Generator for channel 1 generates 10

packets which are transmitted to the 10-Gigabit Ethernet MAC IP core. The packets are

looped back on the PHY and become receive packets on Channel 0. The test bench waits to

receive the 10 packets on each channel without errors and then ends the simulation with a

Simulation Passed

message. Simulating the AXI UART Lite IP and MicroBlaze processor

subsystem takes a lot of time. In order to speed up simulation the Traffic Generator and

Monitor block is not configured using its AXI4-Lite interface connected to the MicroBlaze

processor subsystem. The Traffic Generator and Monitor block provides a port tg_config to

configure the block. This port is used only for simulation.

this port.

The test bench for the 10GBASE-KR TRD is available at:

<working_dir>/kcu1250_10gbasekr_trd/hardware/sources/testbench/tb.v

.

IMPORTANT:

Before running a simulation, the kcu1250_10gbasekr_ref_design project must be open

and

Generate the Hardware Bitstream

must be executed.

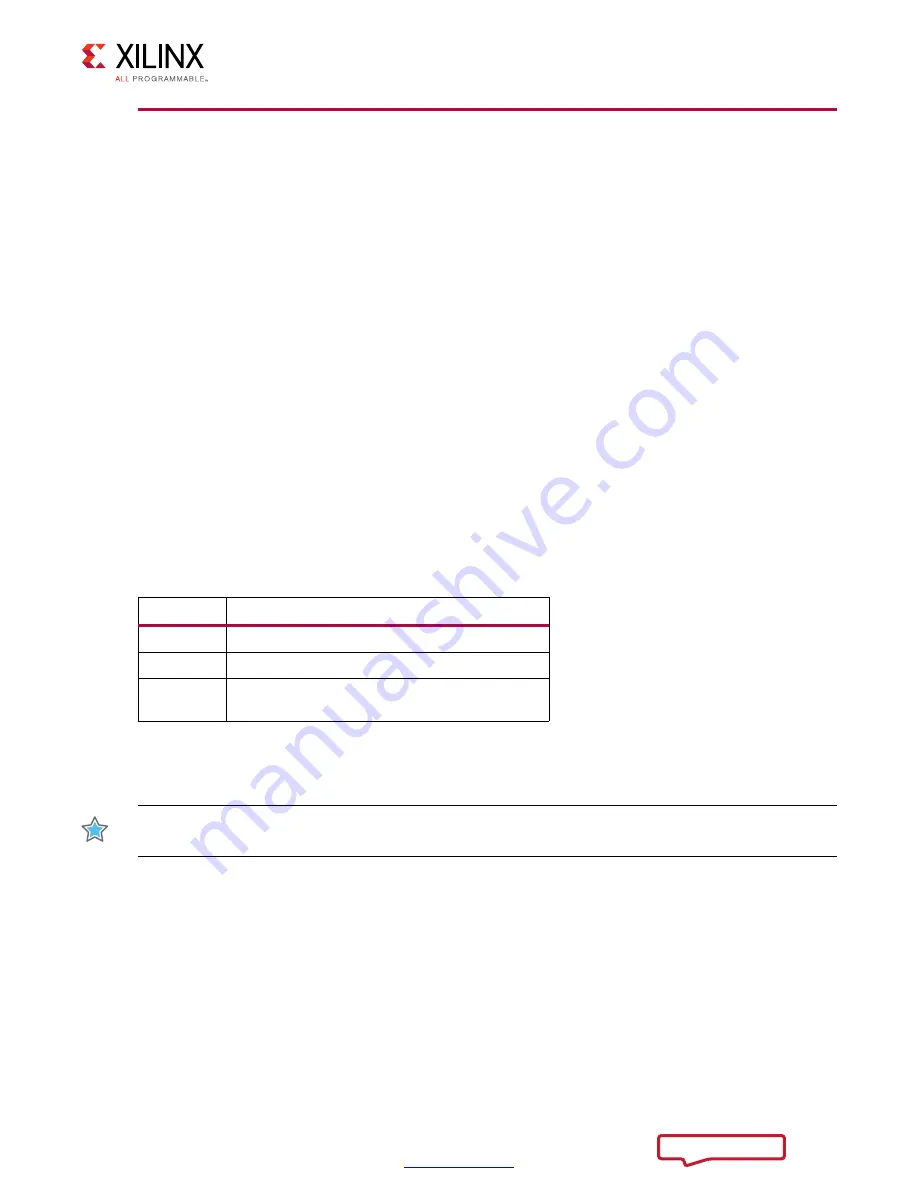

Table 4-1:

Traffic Generator Configuration Port

Bit Position

Description

0

Enable loopback for external generator mode.

1

Enable generator for internal generator mode.

31:16

Ethernet frame data payload size.

Allowed values (46 bytes to 1,500 bytes).