10GBASE-KR Ethernet TRD

74

UG1058 (v2017.1) April 19, 2017

Chapter 5:

Reference Design Details

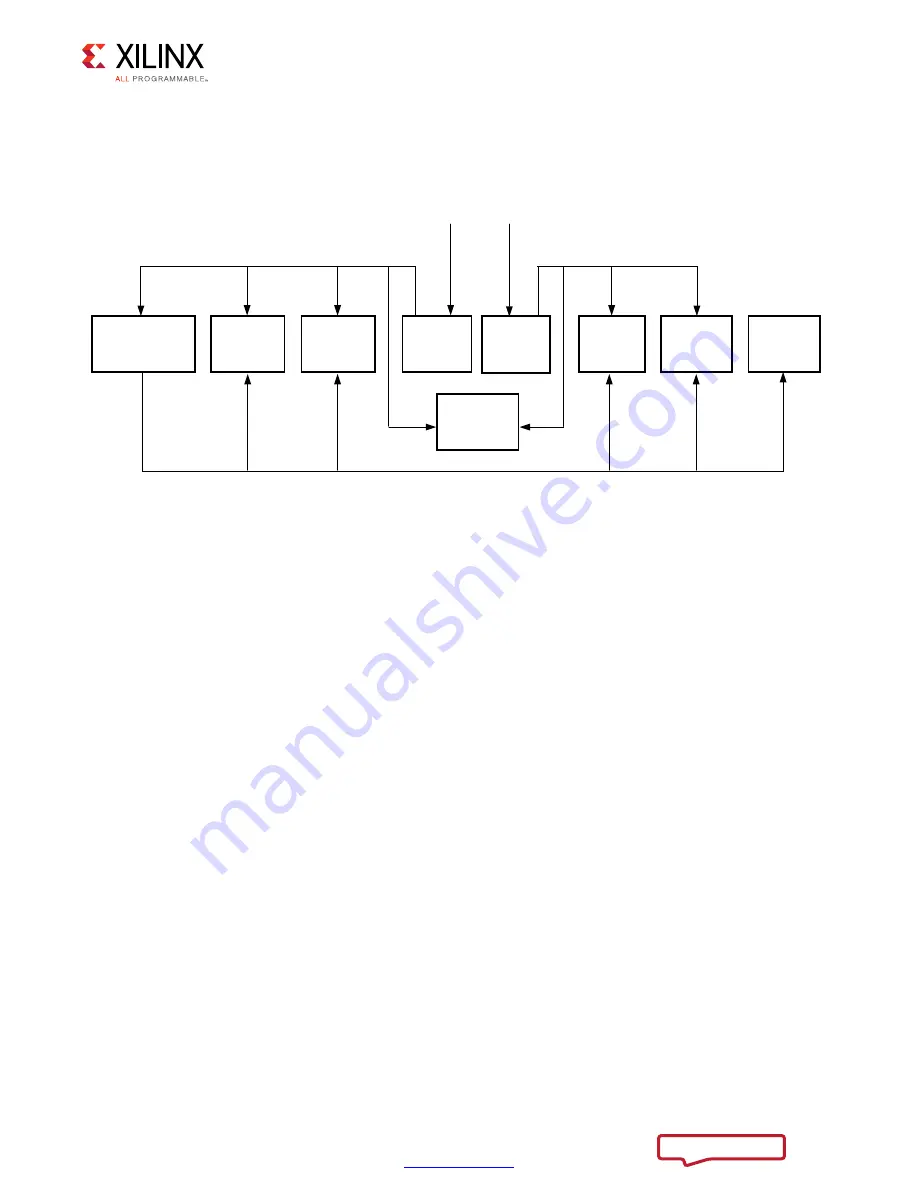

channel 0 156.25 MHz clock. The single ended 156.25 MHz clocks from both channels are

routed to the eye scan system.

shows the clock distribution.

An external reset (a debounced DIP switch) drives the channel 0 10-Gigabit Ethernet

PCS/PMA IP core, the 10-Gigabit Ethernet MAC IP core and the Processor System Reset IP

core in the processor system. This reset also drives the eye scan system.

Another external reset dip switch drives the Channel 1 10-Gigabit Ethernet PCS/PMA IP

core, the 10-Gigabit Ethernet MAC IP core and the Traffic Generator and Monitor block.

X-Ref Target - Figure 5-7

Figure 5-7:

Clock Distribution

CH1 MAC

CH1 PHY

CH0 PHY

CH0 Traffic

Gen-Mon

CH0 MAC

s_axi_clk

CH1

Traffic

Gen-Mon

AXI

UARTLITE

MicroBlaze

Subsytem and

AXI Interconnect

s_axi_clk

s_axi_clk

s_axi_clk

s_axi_clk

156.25 MHz

156.25 MHz

Differential Clock

156.25 MHz

Differential Clock

156.25 MHz CH0

156.25 MHz CH1

Eyescan

System

X18485-120716