AXI Bridge for PCI Express v2.4

35

PG055 June 4, 2014

Chapter 2:

Product Specification

Root Port MSI Base Register 1 (Offset 0x14C)

The Root Port MSI Base register contains the upper 32-bits of the 64-bit MSI address

(described in

).

For EP configurations, read returns zero.

Root Port MSI Base Register 2 (Offset 0x150)

The Root Port MSI Base register 2 (described in

) sets the address window in Root

Port cores used for MSI interrupts. MemWr TLPs to addresses in this range are interpreted

as MSI interrupts. MSI TLPS are interpreted based on the address programmed in this

register. The window is always 4 Kb, beginning at the address indicated in this register. For

EP configurations, a read returns zero. However, the AXI Bridge for PCI Express core does

not support MSI-X and multiple vector address, only single MSI is supported.

Root Port Error FIFO Read Register (Offset 0x154)

Reads from this location return queued error (Correctable/Non-fatal/Fatal) messages. Data

from each read follows the format shown in

. For EP configurations, read returns

zero.

Reads are non-destructive. Removing the message from the FIFO requires a write. The write

value is ignored.

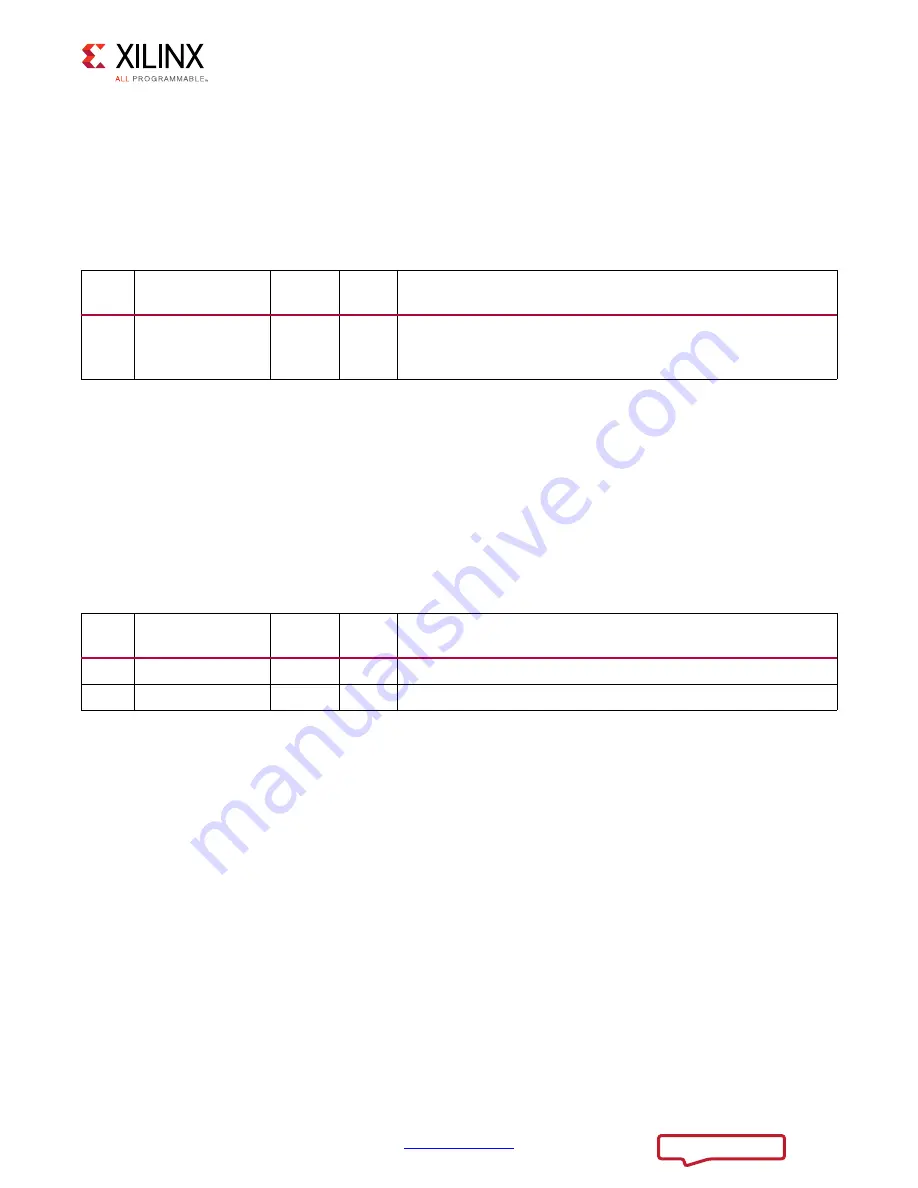

Table 2-17:

Root Port MSI Base Register 1

Bits

Name

Core

Access

Reset

Value

Description

31:0

MSI Base

RW

0

4Kb-aligned address for MSI interrupts. In case of 32-bit MSI,

it returns 0 but captures the upper 32-bits of the MSI address in

case of 64-bit MSI.

Table 2-18:

Root Port MSI Base Register 2

Bits

Name

Core

Access

Reset

Value

Description

11:0

Reserved

RO

0

Reserved

31:12 MSI Base

RW

0

4 Kb-aligned address for MSI interrupts.