AXI Bridge for PCI Express v2.4

36

PG055 June 4, 2014

Chapter 2:

Product Specification

Root Port Interrupt FIFO Read Register 1 (Offset 0x158)

Reads from this location return queued interrupt messages. Data from each read follows the

format shown in

. For MSI interrupts, the message payload is presented in the

Root Port Interrupt FIFO Read 2 register. The interrupt-handling flow should be to read this

register first, immediately followed by the Root Port Interrupt FIFO Read 2 register. For

non-Root Port cores, reads return zero.

Note:

Reads are non-destructive. Removing the message from the FIFO requires a write to either

this register or the Root Port Interrupt FIFO Read 2 register. The write value is ignored.

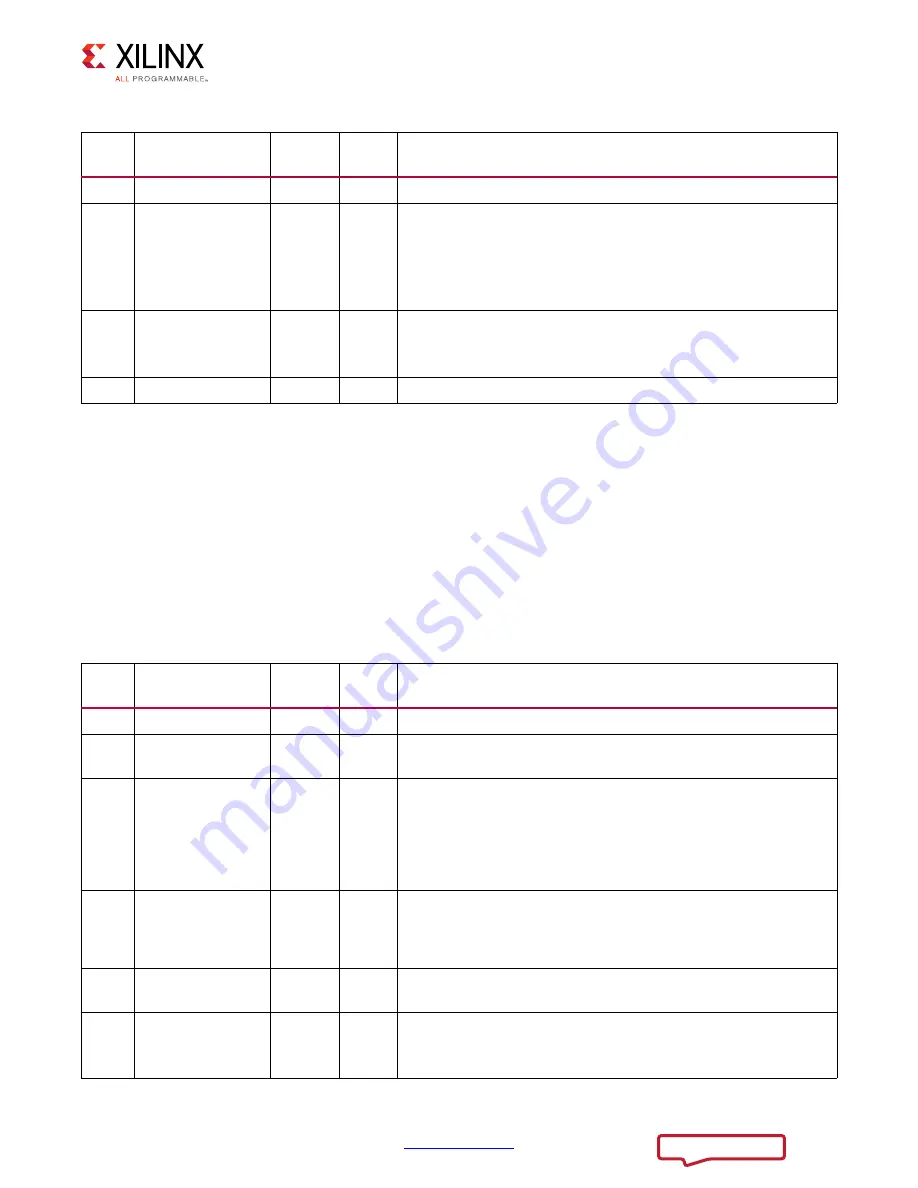

Table 2-19:

Root Port Error FIFO Read Register

Bits

Name

Core

Access

Reset

Value

Description

15:0

Requester ID

RWC

0

Requester ID belonging to the requester of the error message.

17:16 Error Type

RWC

0

Indicates the type of the error.

00b: Correctable

01b: Non-Fatal

10b: Fatal

11b: Reserved

18

Error Valid

RWC

0

Indicates whether read succeeded.

1b: Success

0b: No message to read

31:19 Reserved

RO

0

Reserved

Table 2-20:

Root Port Interrupt FIFO Read Register 1

Bits

Name

Core

Access

Reset

Value

Description

15:0

Requester ID

RWC

0

Requester ID belonging to the requester of the error message.

26:16 MSI Address

RWC

0

For MSI interrupts, contains address bits 12:2 from the TLP

address field.

28:27 Interrupt Line

RWC

0

Indicates interrupt line used.

00b: INTA

01b: INTB

10b: INTC

11b: INTD

For MSI, this field is set to 00b and should be ignored.

29

Interrupt Assert

RWC

0

Indicates assert or deassert for INTx.

1b: Assert

0b: Deassert

For MSI, this field is set to 0b and should be ignored.

30

MSI Interrupt

RWC

0

Indicates whether interrupt is MSI or INTx.

1b = MSI, 0b = INTx.

31

Interrupt Valid

RWC

0

Indicates whether read succeeded.

1b: Success

0b: No interrupt to read