AXI Bridge for PCI Express v2.4

41

PG055 June 4, 2014

Chapter 2:

Product Specification

(C_INCLUDE_RC = 0), the underlying Integrated Block configuration space and the core

memory map are available at the beginning of the memory space. The memory space looks

like a simple PCI Express configuration space. When the AXI Bridge for PCIe is configured

for RC (C_INCLUDE_RC = 1), the same is true, but it also looks like an ECAM access to

primary bus, Device 0, Function 0.

When the AXI Bridge for PCI Express core is configured as a Root Port, the reads and writes

of the local ECAM are Bus 0. Because the FPGA only has a single Integrated Block for PCIe

core, all local ECAM operations to Bus 0 return the ECAM data for Device 0, Function 0.

Configuration write accesses across the PCI Express bus are non-posted writes and block

the AXI4-Lite interface while they are in progress. Because of this, system software is not

able to service an interrupt if one were to occur. However, interrupts due to abnormal

terminations of configuration transactions can generate interrupts. ECAM read transactions

block subsequent Requester read TLPs until the configuration read completions packet is

returned to allow unique identification of the completion packet.

Unsupported Memory Space

Advanced Error Reporting (AER) is not supported in the AXI Bridge for PCI Express core. The

AER register space is not accessible in the AXI Bridge for PCI Express memory mapped

space.

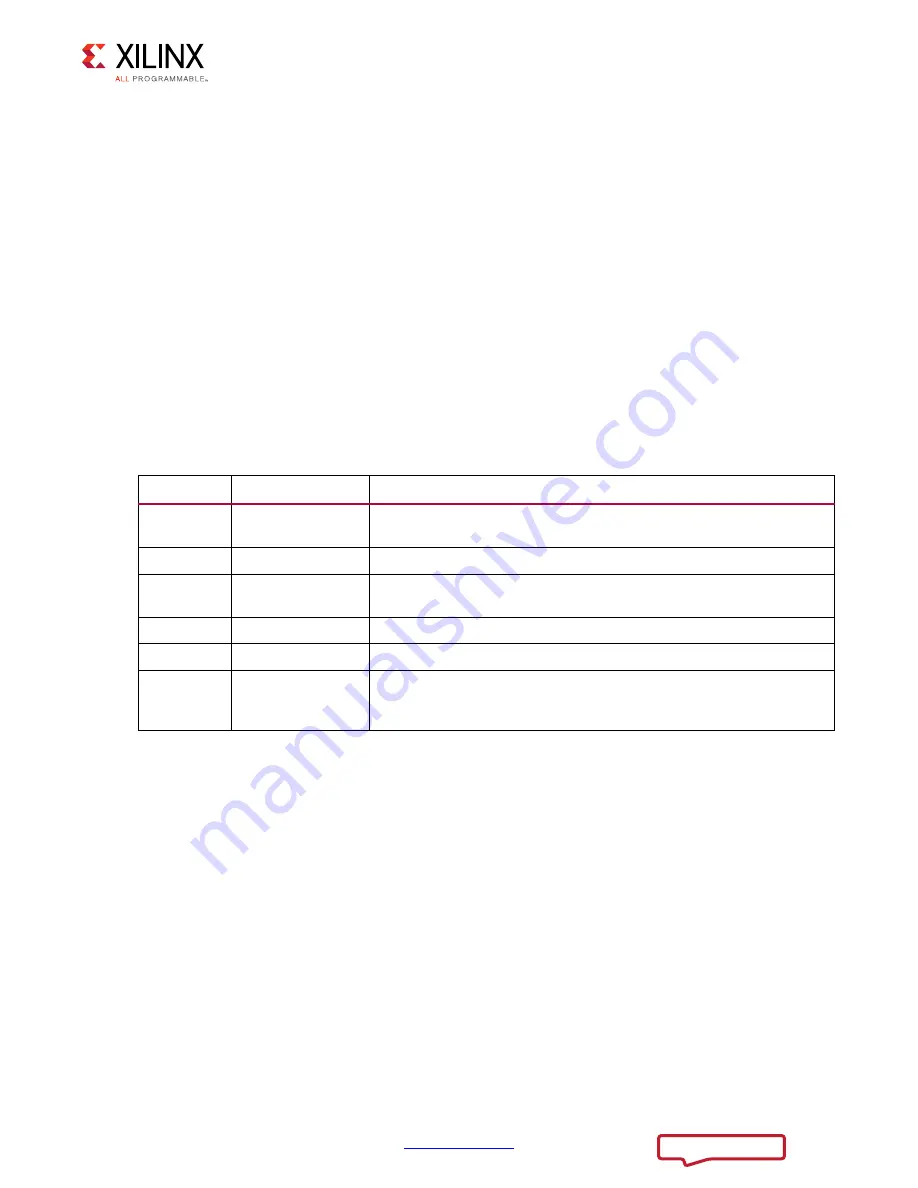

Table 2-26:

ECAM Addressing

Bits

Name

Description

1:0

Byte Address

Ignored for this implementation. The S_AXI_CTL_WSTRB[3:0] signals

define byte enables for ECAM accesses.

7:2

Register Number

Register within the configuration space to access.

11:8

Extended Register

Number

Along with Register Number, allows access to PCI Express Extended

Configuration Space.

14:12

Function Number

Function Number to completer.

19:15

Device Number

Device Number to completer.

(20+n-1):20 Bus Number

Bus Number, 1 <=

n

<= 8.

n

is the number of bits available for Bus

Number as derived from core parameters C_INCLUDE_RC,

C_BASEADDR, and C_HIGHADDR.