AXI Bridge for PCI Express v2.4

45

PG055 June 4, 2014

Chapter 3:

Designing with the Core

The MMCM generates the following clocks for PCIe solution wrapper:

• clk_125mhz - 125 MHz clock.

• clk_250mhz - 250 MHz clock.

• userclk - 62.5 MHz / 125 MHz / 250 MHz clock, depending on selected PCIe core lane

width, link speed, and AXI interface width.

• userclk2 – 250 MHz / 500 MHz clock, depending on selected PCIe core link speed.

• oobclk – 50 MHz clock.

The other cores/logic present in the user design can use any of the MMCM outputs listed

above.

The MMCM instantiated in the PCIe example design has two unconnected outputs:

clkout5

, and

clkout6

. You can use those outputs to generate other desired clock

frequencies by selecting the appropriate CLKOUT5_DIVIDE and CLKOUT6_DIVIDE

parameters for MMCM.

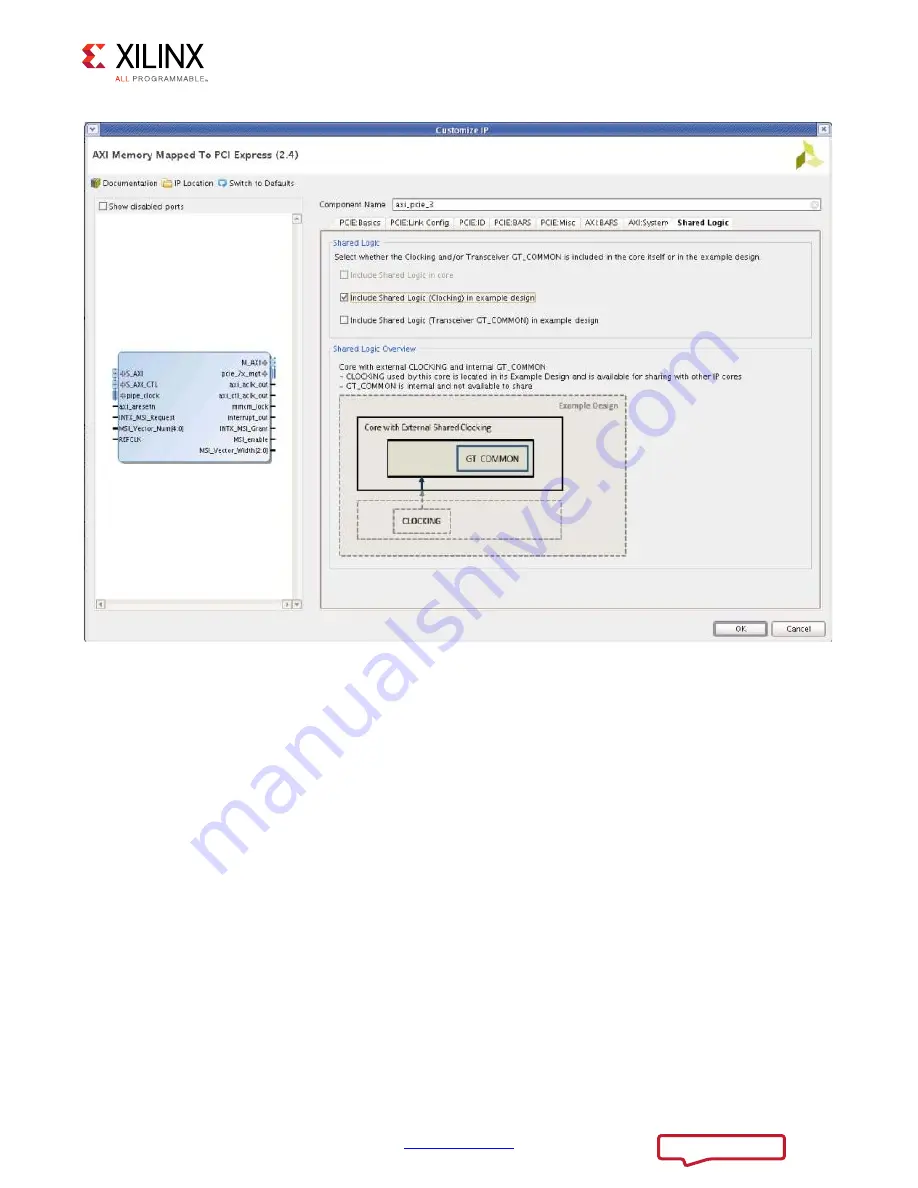

X-Ref Target - Figure 3-3

Figure 3-3:

Shared Clocking