AXI Bridge for PCI Express v2.4

72

PG055 June 4, 2014

Chapter 4:

Design Flow Steps

All BAR registers share these options:

•

Checkbox

: Click the checkbox to enable the BAR; deselect the checkbox to disable the

BAR.

•

Type

: BARs can be Memory apertures only.

°

Memory

: Memory BARs can be either 64-bit or 32-bit. Prefetch is enabled for

64-bit and not enabled for 32-bit. When a BAR is set as 64 bits, it uses the next BAR

for the extended address space, making it inaccessible.

•

Size

: The available Size range depends on the PCIe® Device/Port Type and the Type of

BAR selected.

lists the available BAR size ranges.

•

Value

: The value assigned to the BAR based on the current selections.

For more information about managing the Base Address Register settings, see

Base Address Register Settings

.

Managing Base Address Register Settings

Memory indicates that the address space is defined as memory aperture. The base address

register only responds to commands that access the specified address space. Generally,

memory spaces less than 4 KB in size should be avoided.

Disabling Unused Resources

For best results, disable unused base address registers to conserve system resources. A base

address register is disabled by deselecting unused BARs in the Vivado IDE.

PCIe Miscellaneous

The PCIe Misc screen is shown in

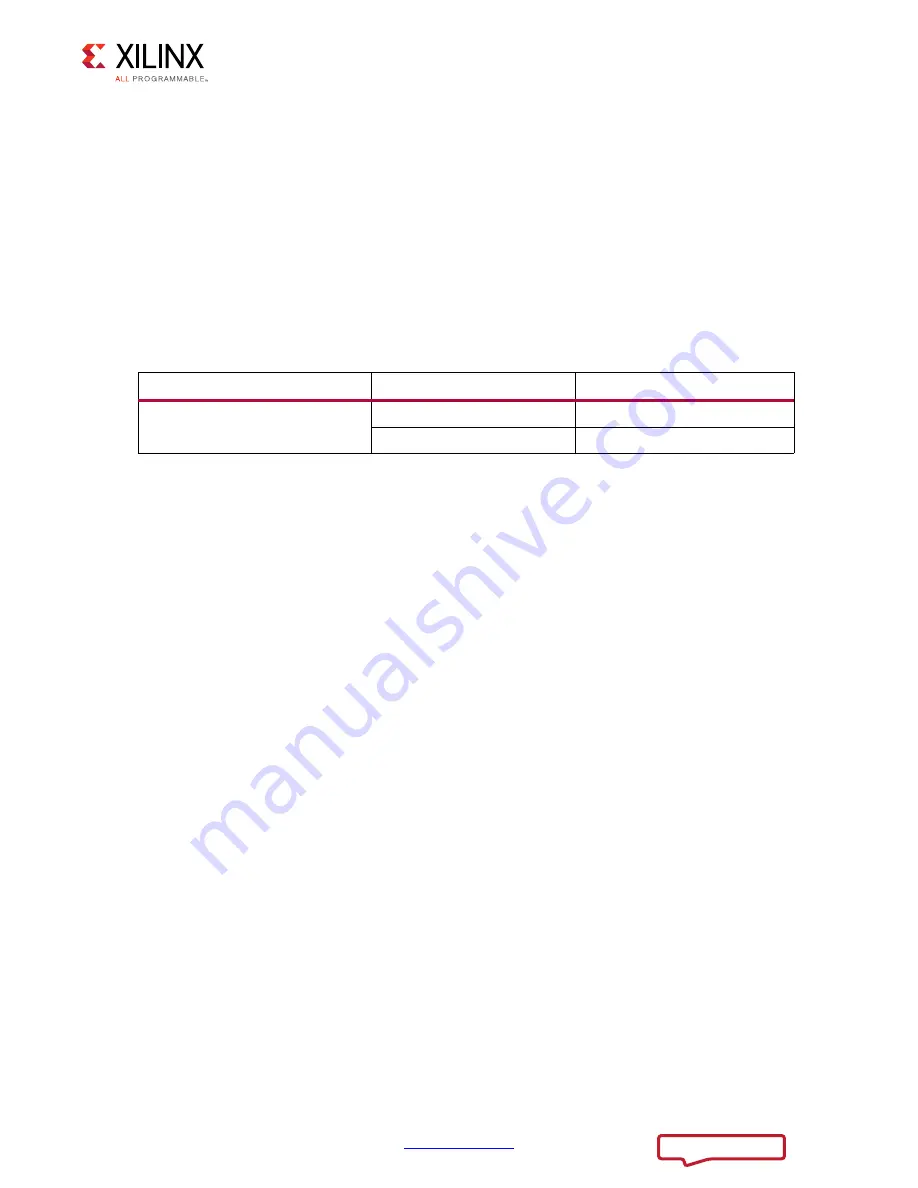

Table 4-3:

BAR Size Ranges for Device Configuration

PCIe Device/Port Type

BAR Type

BAR Size Range

PCI Express Endpoint

32-bit Memory

128 Bytes - 2 Gigabytes

64-bit Memory

128 Bytes - 8 Exabytes