AXI Bridge for PCI Express v2.4

104

PG055 June 4, 2014

Appendix B:

Debugging

Interface Debug

AXI4-Lite Interfaces

Read from a register that does not have all 0s as a default to verify that the interface is

functional. Output

s_axi_arready

asserts when the read address is valid and output

s_axi_rvalid

asserts when the read data/response is valid. If the interface is

unresponsive ensure that the following conditions are met.

• The

axi_ctl_aclk

and

axi_ctl_aclk_out

clock inputs are connected and

toggling.

• The interface is not being held in reset, and

axi_aresetn

is an active-Low reset.

• Ensure that the main core clocks are toggling and that the enables are also asserted.

• Has a simulation been run? Verify in simulation and/or a Vivado lab tools capture that

the waveform is correct for accessing the AXI4-Lite interface.

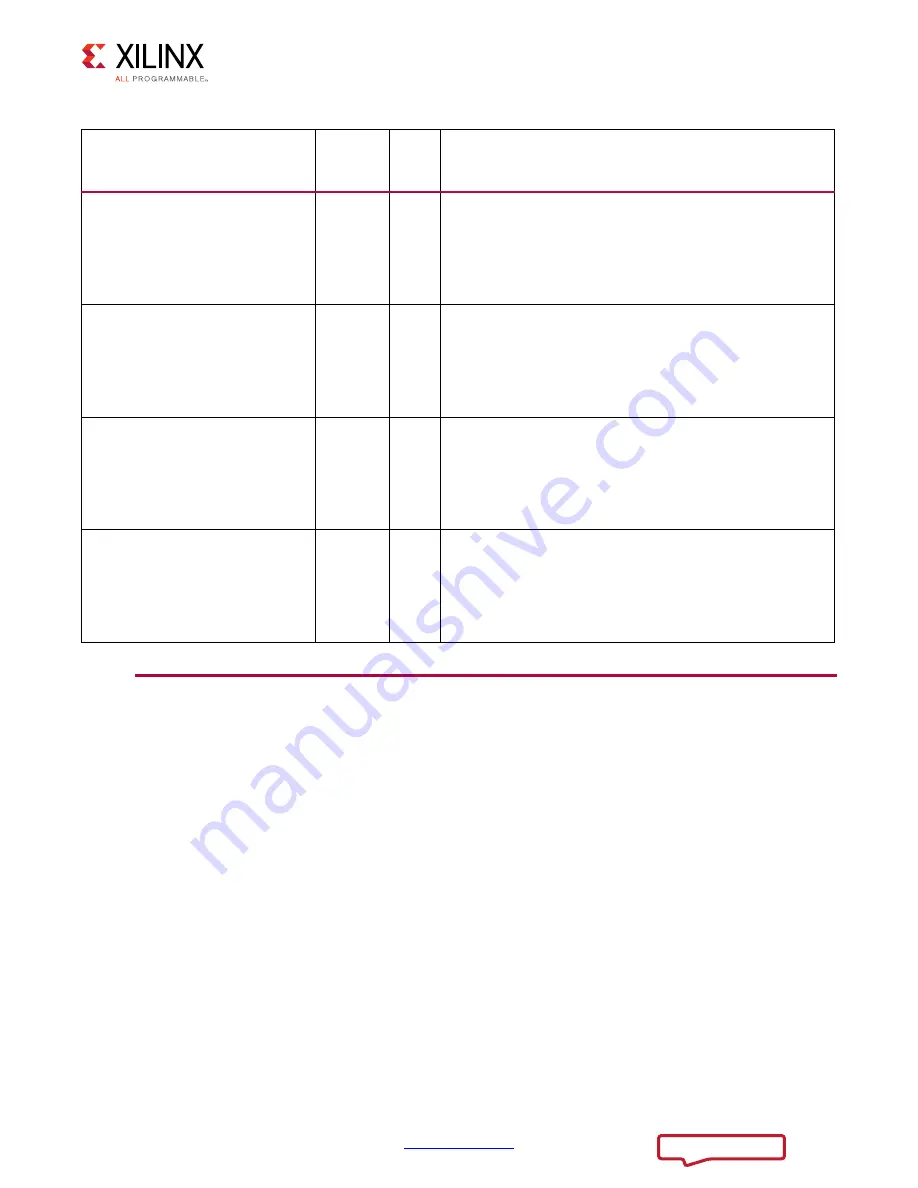

PIPE_DEBUG_6/gt_rxcommadet

O

Generic debug ports to assist debug. These generic debug

ports bring out internal PIPE Wrapper signals, such as raw

GT signals. DEBUG_0 to DEBUG_9 are intended for per

lane signals. The bus width of these generic debug ports

depends on the number of lanes configured in the

wrapper.

PIPE_DEBUG_7/gt_rdy

O

Generic debug ports to assist debug. These generic debug

ports bring out internal PIPE Wrapper signals, such as raw

GT signals. DEBUG_0 to DEBUG_9 are intended for per

lane signals. The bus width of these generic debug ports

depends on the number of lanes configured in the

wrapper.

PIPE_DEBUG_8/user_rx_converge

O

Generic debug ports to assist debug. These generic debug

ports bring out internal PIPE Wrapper signals, such as raw

GT signals. DEBUG_0 to DEBUG_9 are intended for per

lane signals. The bus width of these generic debug ports

depends on the number of lanes configured in the

wrapper.

PIPE_DEBUG_9/PIPE_TXELECIDLE

O

Generic debug ports to assist debug. These generic debug

ports bring out internal PIPE Wrapper signals, such as raw

GT signals. DEBUG_0 to DEBUG_9 are intended for per

lane signals. The bus width of these generic debug ports

depends on the number of lanes configured in the

wrapper.

Table B-1:

Ports Used for Transceiver Debug

(Cont’d)

Port

Direction Width

Description