AXI Bridge for PCI Express v2.4

15

PG055 June 4, 2014

Chapter 2:

Product Specification

Bridge Parameters

Because many features in the AXI Bridge for PCI Express core design can be parameterized,

you are able to uniquely tailor the implementation of the core using only the resources

required for the desired functionality. This approach also achieves the best possible

performance with the lowest resource usage.

The parameters defined for the AXI Bridge for PCI Express are shown in

.

s_axi_ctl_rvalid

O Slave read valid

s_axi_ctl_rready

I

Slave read ready

MSI Signals

intx_msi_request

I

Legacy interrupt input (see

c_interrupt_pin

) when

msi_enable

= 0.

Initiates a MSI write request when

msi_enable

= 1.

Intx_msi_request

is asserted for one clock period.

intx_msi_grant

O

Indicates legacy interrupt/MSI grant signal. The

intx_msi_grant

signal is asserted for one clock period

when the interrupt is accepted by the PCIe core.

msi_enable

O Indicates when MSI is enabled.

msi_vector_num [4:0]

I

Indicates MSI vector to send when writing a MSI write

request.

msi_vector_width [2:0]

O Indicates the size of the MSI field (the number of MSI

vectors allocated to the device).

PCIe Interface

pci_exp_rxp[c_no_of_lanes-1: 0]

I

PCIe RX serial interface

pci_exp_rxn[c_no_of_lanes-1: 0]

I

PCIe RX serial interface

pci_exp_txp[c_no_of_lanes-1: 0]

O PCIe TX serial interface

pci_exp_txn[c_no_of_lanes-1:0]

O PCIe TX serial interface

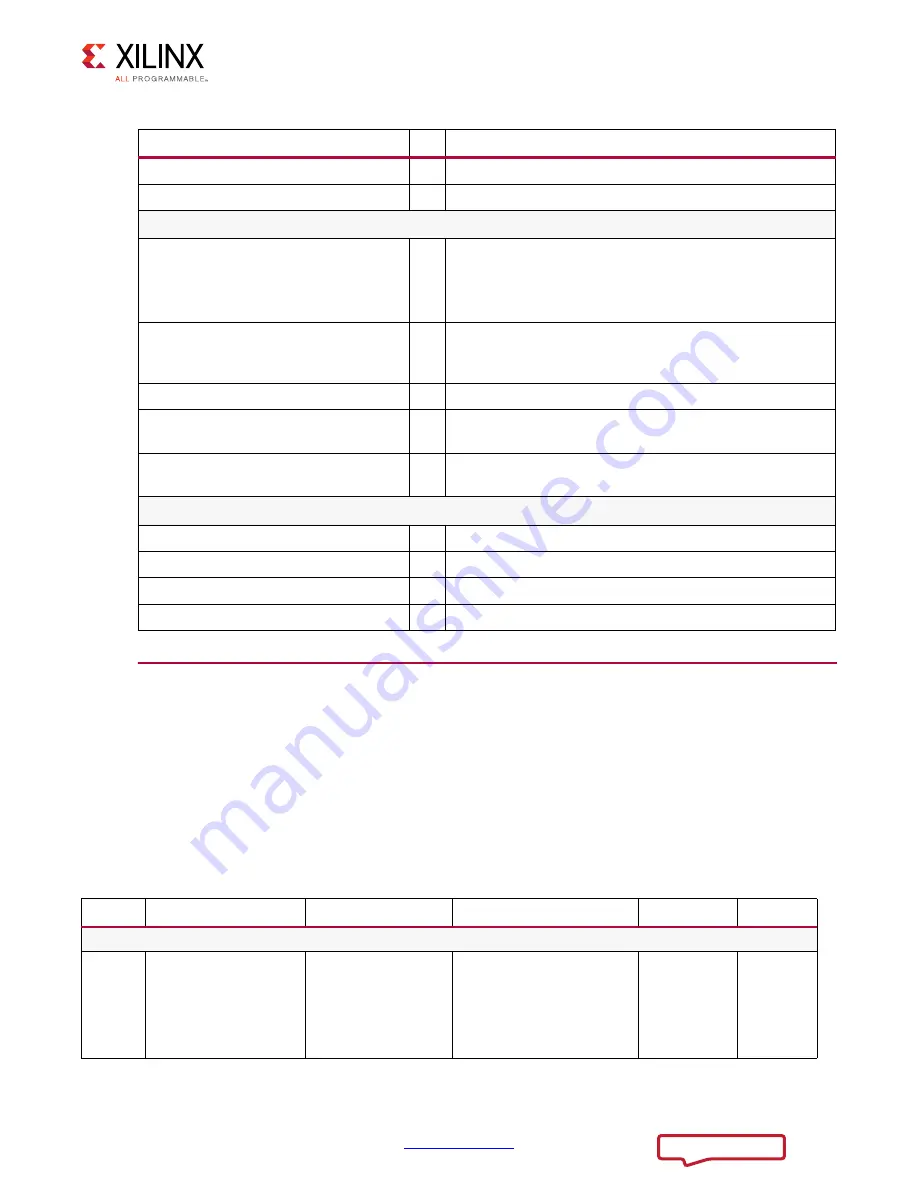

Table 2-3:

Top-Level Interface Signals

(Cont’d)

Signal Name

I/O Description

Table 2-4:

Top-Level Parameters

Generic

Parameter Name

Description

Allowable Values

Default Value VHDL Type

Bridge Parameters

C_PCIE_BLK_LOCN

PCIe integrated

block location

within FPGA

0: X0Y0

1: X0Y1

2: X0Y2

3: X1Y0

4: X1Y1

0

String