AXI Bridge for PCI Express v2.4

24

PG055 June 4, 2014

Chapter 2:

Product Specification

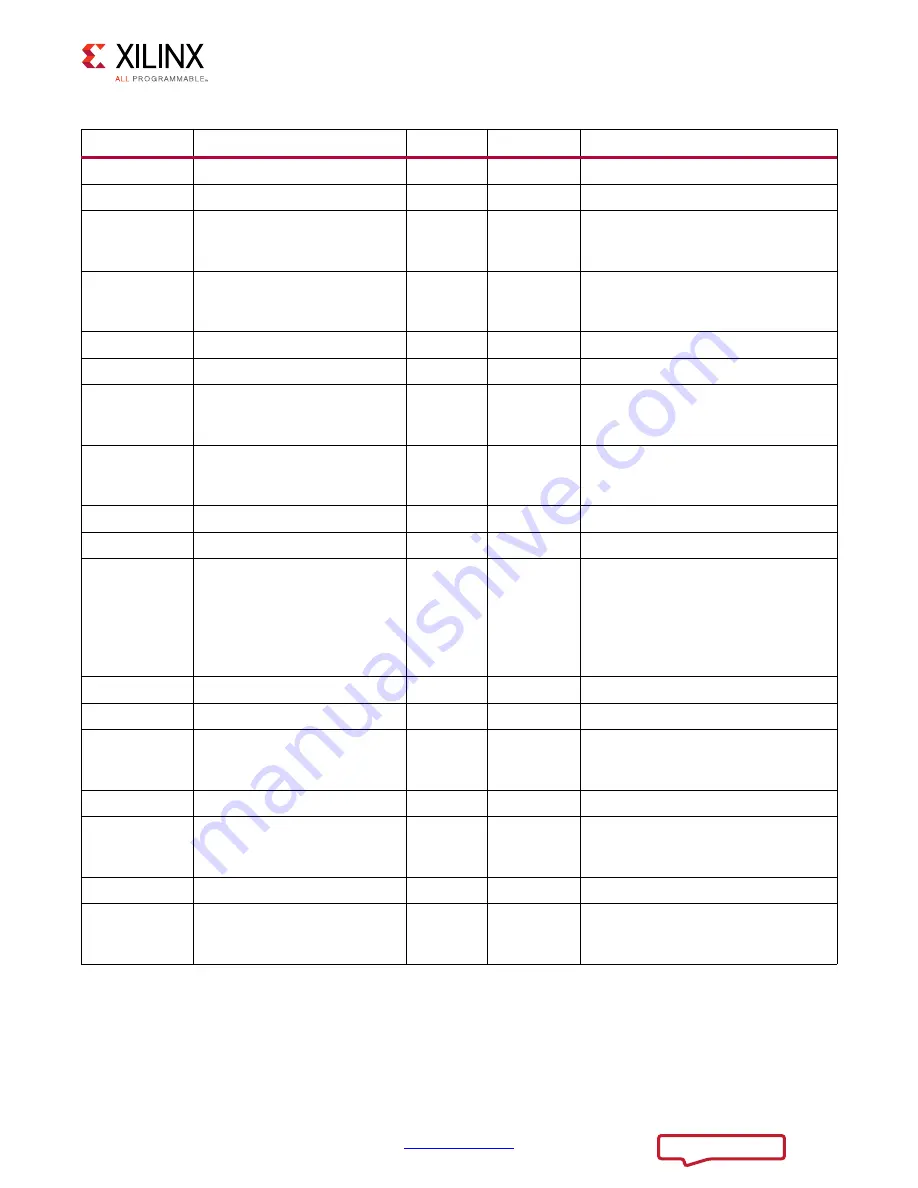

G21

C_AXIBAR_AS_3

G22

C_AXIBAR2PCIEBAR_3

,

Meaningful when G4 = 1.

G23

C_AXIBAR_4

G23 and G24 define the range in

AXI-memory space that is responded

to by this device (AXIBAR)

G24

C_AXIBAR_HIGHADDR_4

,

G23 and G24 define the range in

AXI-memory space that is responded

to by this device (AXIBAR)

G25

C_AXIBAR_AS_4

G26

C_AXIBAR2PCIEBAR_4

,

Meaningful if G4 = 1.

G27

C_AXIBAR_5

G27 and G28 define the range in

AXI-memory space that is responded

to by this device (AXIBAR)

G28

C_AXIBAR_HIGHADDR_5

,

G27 and G28 define the range in

AXI-memory space that is responded

to by this device (AXIBAR)

G29

C_AXIBAR_AS_5

G30

C_AXIBAR2PCIEBAR_5

,

Meaningful if G4 = 1.

G31

C_PCIEBAR_NUM

-

If G31 = 1, then G32, G33 are

enabled.

If G31 = 2, then G32 - G36 are

enabled.

If G31 = 3, then G32 - G38 are

enabled

G32

C_PCIEBAR_AS

G33

C_PCIEBAR_LEN_0

G34

C_PCIEBAR2AXIBAR_0

,

Only the high-order bits above the

length defined by G33 are

meaningful.

G35

C_PCIEBAR_LEN_1

G36

C_PCIEBAR2AXIBAR_1

,

Only the high-order bits above the

length defined by G35 are

meaningful.

G37

C_PCIEBAR_LEN_2

G38

C_PCIEBAR2AXIBAR_2

,

Only the high-order bits above the

length defined by G37 are

meaningful.

Table 2-5:

Parameter Dependencies

(Cont’d)

Generic

Parameter

Affects

Depends

Description