AXI Bridge for PCI Express v2.4

26

PG055 June 4, 2014

Chapter 2:

Product Specification

Memory Map

The memory map shown in

shows the address mapping for the AXI Bridge for PCI

Express core. These registers are described in more detail in the following section. All

registers are accessed through the AXI4-Lite Control Interface and are offset from

C_BASEADDR. During a reset, all registers return to default values.

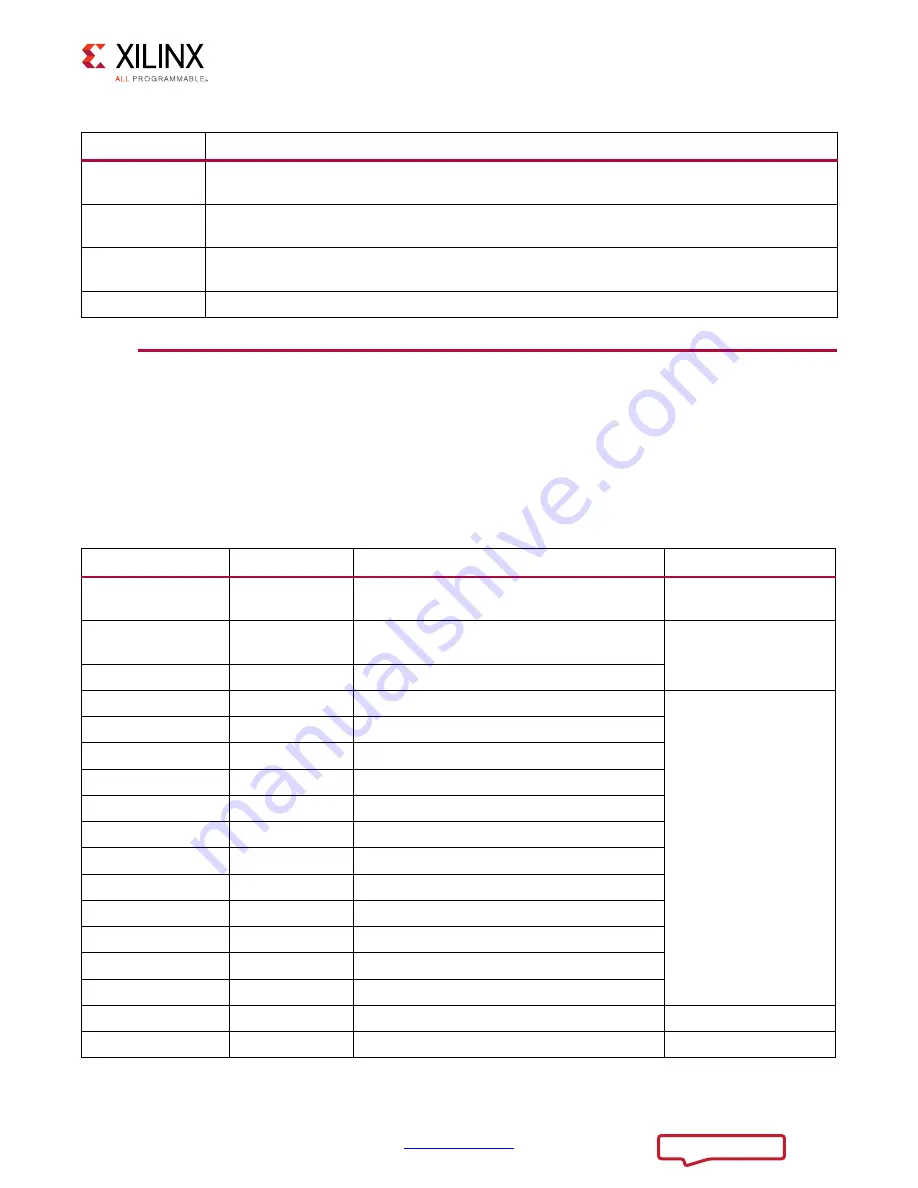

Table 2-6:

Silicon Version Specification

C_FAMILY

C_PCIE_USE_MODE

Kintex-7

1.1 = for Kintex-7 325T IES (initial silicon)

3.0 = for GES (general silicon)

Virtex-7

1.1 = for Virtex-7 485T IES (initial silicon)

3.0 = for GES and Production (general silicon and Production silicon)

Artix-7

1.0 = for IES (initial silicon) as well as GES and Production (General silicon and Production

silicon) to use latest serial transceiver wrappers (only allowable value)

Zynq

Not applicable. (set internally = 3.0)

Table 2-7:

Register Memory Map

Accessibility

Offset

Contents

Location

RO - EP, R/W - RC

0x000 - 0x124

PCIe Configuration Space Header

Part of integrated PCIe

configuration space.

RO

0x128

Vendor-Specific Enhanced Capability (VSEC)

Capability

VSEC of integrated PCIe

configuration space.

RO

0x12C

VSEC Header

RO

0x130

Bridge Info

AXI bridge defined

memory-mapped

register space.

RO - EP, R/W - RC

0x134

Bridge Status and Control

R/W

0x138

Interrupt Decode

R/W

0x13C

Interrupt Mask

RO - EP, R/W - RC

0x140

Bus Location

RO

0x144

Physical-Side Interface (PHY) Status/Control

RO - EP, R/W - RC

0x148

Root Port Status/Control

RO - EP, R/W - RC

0x14C

Root Port MSI Base 1

RO - EP, R/W - RC

0x150

Root Port MSI Base 2

RO - EP, R/W - RC

0x154

Root Port Error FIFO Read

RO - EP, R/W - RC

0x158

Root Port Interrupt FIFO Read 1

RO - EP, R/W - RC

0x15C

Root Port Interrupt FIFO Read 2

RO

0x160 - 0x1FF

Reserved (zeros returned on read)

RO

0x200

VSEC Capability 2