AXI Bridge for PCI Express v2.4

37

PG055 June 4, 2014

Chapter 2:

Product Specification

Root Port Interrupt FIFO Read Register 2 (Offset 0x15C)

Reads from this location return queued interrupt messages. Data from each read follows the

format shown in

. For MSI interrupts, the message payload is presented in this

register, while the header information is presented in the Root Port Interrupt FIFO Read 1

register. The interrupt-handling flow should be to read the Root Port Interrupt FIFO Read 1

register first, immediately followed by this register. For non-Root Port cores, reads return 0.

For INTx interrupts, reads return zero.

Note:

Reads are non-destructive. Removing the message from the FIFO requires a write to either

this register or the Root Port Interrupt FIFO Read 1 register (write value is ignored).

VSEC Capability Register 2 (Offset 0x200)

The VSEC capability register (described in

) allows the memory space for the core

to appear as though it is a part of the underlying integrated block PCIe configuration space.

The VSEC is inserted immediately following the last enhanced capability structure in the

underlying block. VSEC is defined in §7.18 of the

PCI Express Base Specification, v1.1

(§7.19

.

This register is only included if C_INCLUDE_BAR_OFFSET_REG = 1.

VSEC Header Register 2 (Offset 0x204)

The VSEC Header Register 2 (described in

) provides a unique (within a given

vendor) identifier for the layout and contents of the VSEC structure, as well as its revision

and length.

This register is only included if C_INCLUDE_BAR_OFFSET_REG = 1.

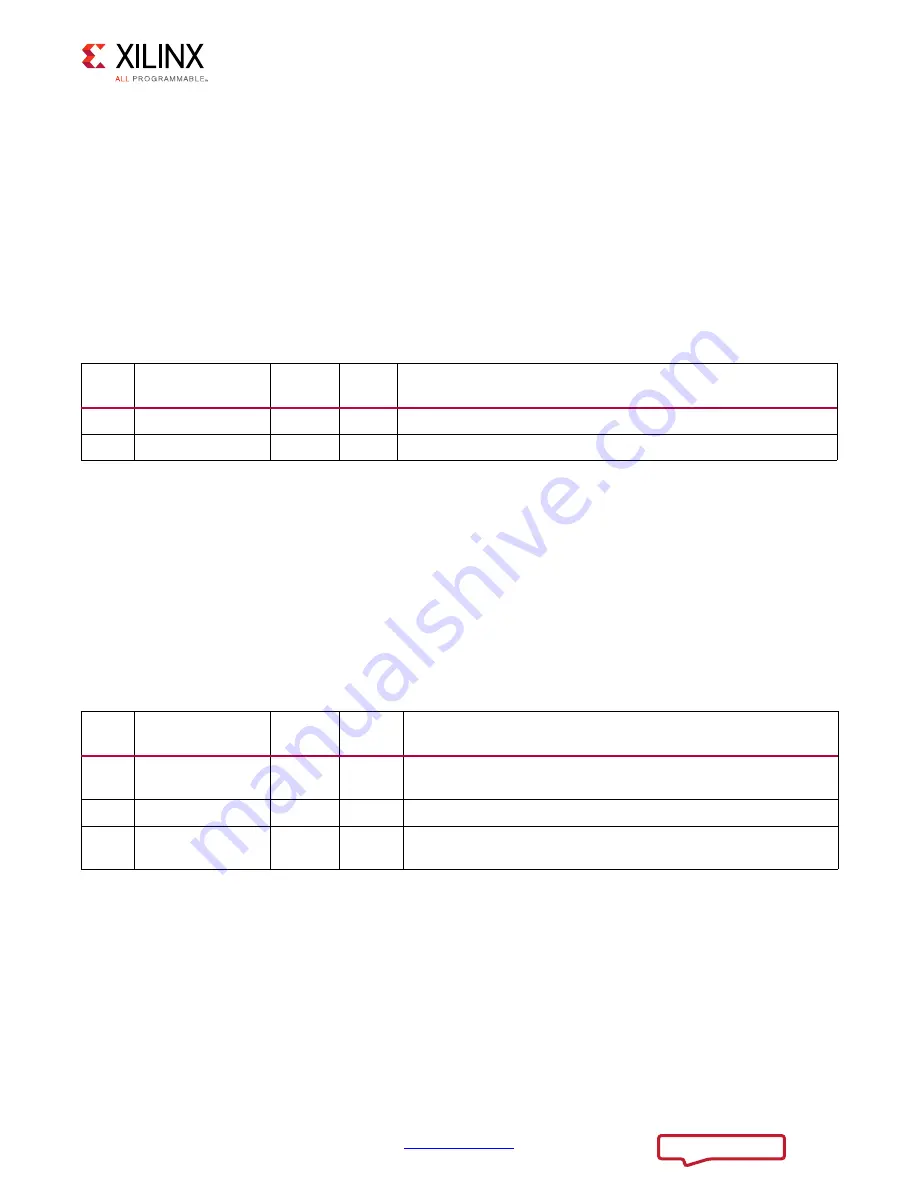

Table 2-21:

Root Port Interrupt FIFO Read Register 2

Bits

Name

Core

Access

Reset

Value

Description

15:0

Message Data

RWC

0

Payload for MSI messages.

31:16 Reserved

RO

0

Reserved

Table 2-22:

VSEC Capability Register 2

Bits

Name

Core

Access

Reset

Value

Description

15:0

VSEC Capability ID

RO

0x000B PCI-SIG defined ID identifying this Enhanced Capability as a

Vendor-Specific capability. Hardcoded to 0x000B.

19:16 Capability Version

RO

0x1

Version of this capability structure. Hardcoded to 0x1.

31:20 Next Capability

Offset

RO

0x000

Offset to next capability.