Ethernet 1000BASE-X PCS/PMA or SGMII v7.0

www.xilinx.com

19

UG145 January 18, 2006

R

Chapter 3

Quick Start Example Design

The quick start steps provided in this chapter let you quickly generate an Ethernet

1000BASE-X PCS/PMA or SGMII core, run the design through implementation with the

Xilinx tools, and simulate the design using the provided demonstration test bench. For

detailed information about the example design, see

Chapter 4, “Detailed Example

Design.”

Overview

The Ethernet 1000BASE-X PCS/PMA example design consists of:

•

Ethernet 1000BASE-X PCS/PMA core netlist

•

Example design HDL top-level and associated HDL files

•

Demonstration test bench to exercise the example design

The Ethernet 1000BASE-X PCS/PMA example design has been tested with Xilinx ISE 8.1i,

Cadence IUS 5.5 and Modelsim® PE/SE 6.1a.

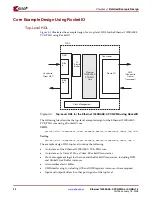

Figure 3-1:

Ethernet 1000BASE-X PCS/PMA Example Design and Test Bench

1000BASE-X

PMA

Monitor

1000BASE-X

PMA

Stimulus

GMII

Stimulus

GMII

Monitor

IOBs

In

IOBs

Out

Ethernet

1000BASE-X

PCS/PMA

Core

Clock Management

FPGA

Testbench

RocketIO

Tx

Elastic

Buffer