ML505/ML506/ML507 Evaluation Platform

www.xilinx.com

UG347 (v3.1.1) October 7, 2009

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development

of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the

Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise,

without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves

the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors

contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with

technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU “AS-IS” WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER

WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY

RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL

DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© 2006–2009 Xilinx, Inc. All rights reserved.

XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. PCI, PCI-SIG,

PCI EXPRESS, PCIE, PCI-X, PCI HOT PLUG, MINI PCI, EXPRESSMODULE, and the PCI, PCI-X, PCI HOT PLUG, and MINI PC design

marks are trademarks, registered trademarks, and/or service marks of PCI-SIG. All other trademarks are the property of their respective

owners.

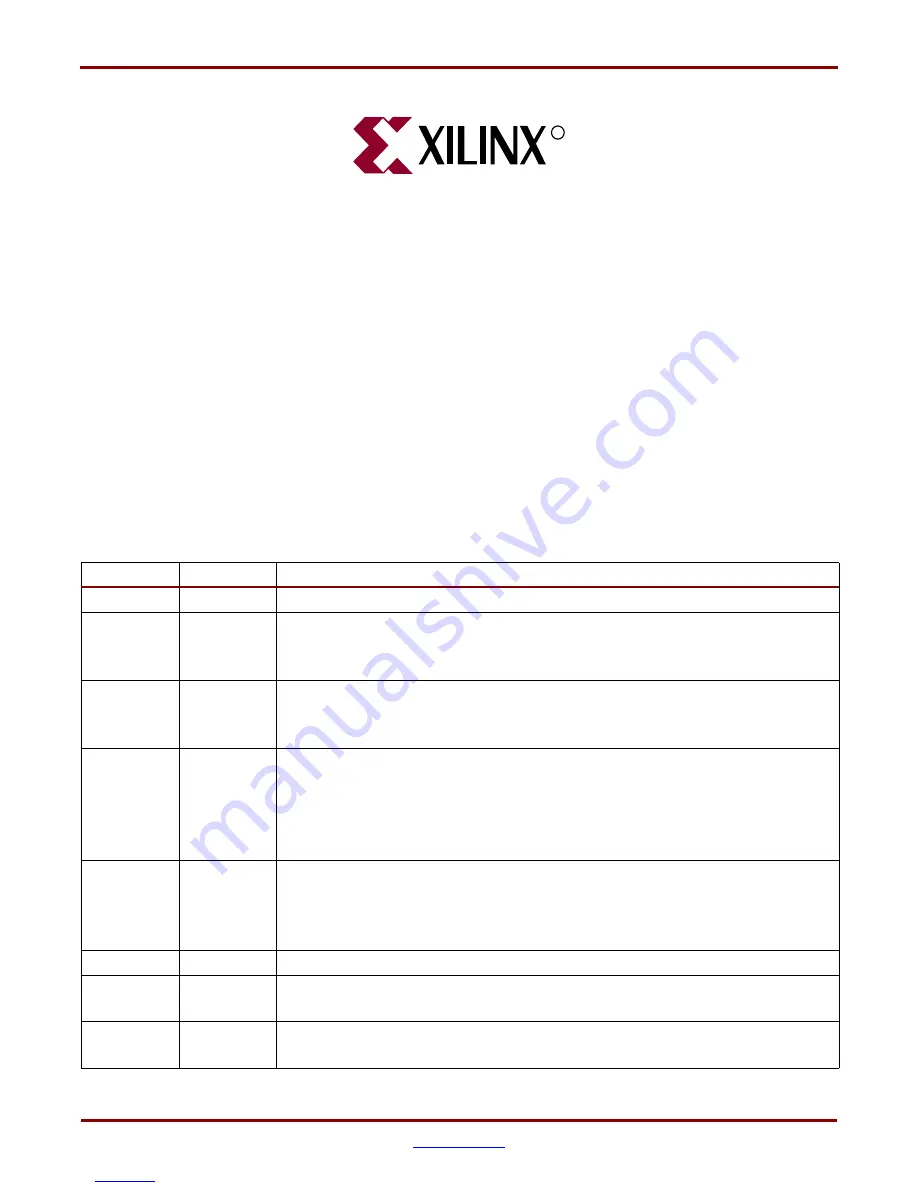

Revision History

The following table shows the revision history for this document.

Date

Version

Revision

11/29/06

1.0

Initial Xilinx release.

12/01/06

1.1

Added

“44. Soft Touch Landing Pad,” page 48

Corrected

Table 1-6, page 21

Added

Table 1-13, page 26

01/09/06

1.2

Added new paragraph to

“36. VGA Input Video Codec,” page 37

Enhanced

Table 1-3, page 19

Corrected

Table 1-31, page 47

02/16/07

2.0

Updated document to include ML506 board

Corrected

Table 1-31, page 47

Enhanced

Figure 1-5, page 34

Expanded

“26. AC Adapter and Input Power Switch/Jack,” page 34

Added

Figure B-1, page 57

03/21/07

2.1

Updated

“Features,” page 11

Swapped

Table 1-3, page 19

with

Table 1-24, page 42

for better placement of information

Updated description for

Table 1-25, page 43

Updated

Table 1-31, page 47

(see table notes)

04/17/07

2.2

Corrected GTP/GTX tile location in

Table 1-24, page 42

06/28/07

2.3

Corrected J5 pin 28 in

Table 1-11, page 25

Updated

Table 1-31, page 47

for XAUI/SRIO support

10/30/07

2.4

Update

Appendix C, “References”Table 1-11, page 25

Added sections on

“MIG Compliance,” page 18

and

“45. System Monitor,” page 49

R

electronic components distributor