50

www.xilinx.com

ML505/ML506/ML507 Evaluation Platform

UG347 (v3.1.1) October 7, 2009

Chapter 1:

ML505/ML506/ML507 Evaluation Platform

R

made as the AUX channels are also used as general-purpose I/O on the XGI connectors

(see

“10. XGI Expansion Headers,” page 22

for additional details). The AUX channels are

still available for use with the System Monitor functions, but they will not attain the

performance level of the dedicated analog input as noted in the

Virtex-5 FPGA System

Monitor User Guide

. Access to the dedicated analog input pairs (VP/VN) is provided

through pins 9 and 10 of the System Monitor Header (J9). See

Table 1-34

.

The Virtex-5 FPGA System Monitor function is built around a 10-bit, 200-kSPS

(kilosamples per second) Analog-to-Digital Converter (ADC). When combined with a

number of on-chip sensors, the ADC is used to measure FPGA physical operating

parameters like on-chip power supply voltages and die temperatures. Access to external

voltages is provided through a dedicated analog-input pair (VP/VN) and 16 user

selectable analog inputs, known as auxiliary analog inputs (VAUXP[15:0], VAUXN[15:0]).

The System Monitor is fully functional on power up, and measurement data can be

accessed via the JTAG port pre-configuration. The Xilinx ChipScope™ Pro tool

[Ref 24]

provides access to the System Monitor over the JTAG port. The System Monitor control

logic implements some common monitoring features. For example, an automatic channel

sequencer allows a user-defined selection of parameters to be automatically monitored,

and user-programmable averaging is enabled to ensure robust noise-free measurements.

The System Monitor also provides user-programmable alarm thresholds for the on-chip

sensors. Thus, if an on-chip monitored parameter moves outside the user-specified

operating range, an alarm logic output becomes active. In addition to monitoring the on-

chip temperature for user-defined applications, the System Monitor issues a special alarm

called Over-Temperature (OT) if the FPGA temperature becomes critical (> 125°C). The

over-temperature signal is deactivated when the device temperature falls below a user-

specified lower limit. If the FPGA power-down feature is enabled, the FPGA enters power

down when the OT signal becomes active. The FPGA powers up again when the alarm is

deactivated.

For additional information about the System Monitor, see

http://www.xilinx.com/systemmonitor

and consult the

Virtex-5 FPGA System Monitor

User Guide

[Ref 14]

.

Table 1-34

shows the System Monitor connections.

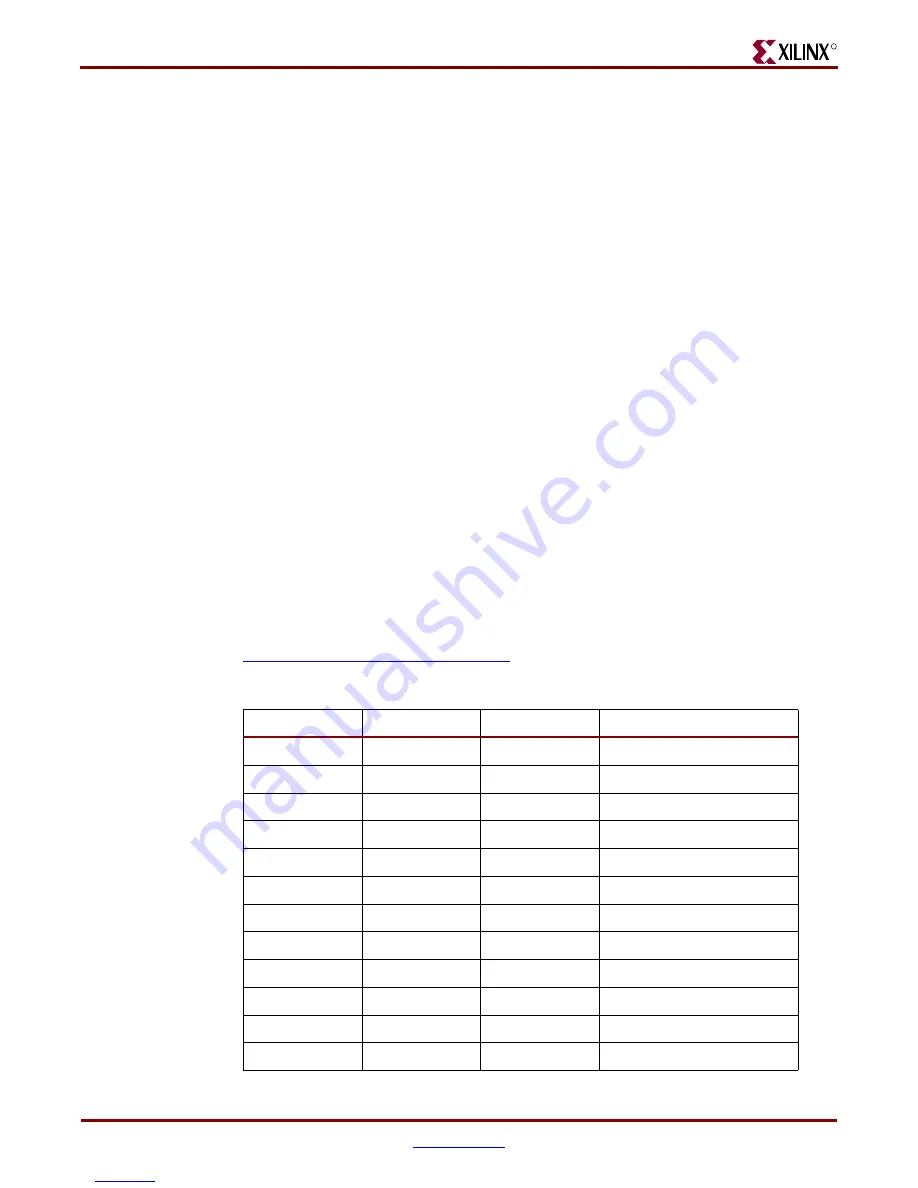

Table 1-34:

System Monitor Connections

External Input

FPGA Pin

Header Pin

Schematic Net Name

VN

V17

J9-10

FPGA_V_N

VP

U18

J9-9

FPGA_V_P

VAUXN[0]

AE34

J4-42

HDR2_42_SM_14_N

VAUXP[0]

AF34

J4-44

HDR2_44_SM_14_P

VAUXN[1]

AE33

J4-46

HDR2_46_SM_12_N

VAUXP[1]

AF33

J4-48

HDR2_48_SM_12_P

VAUXN[2]

AB33

J4-58

HDR2_58_SM_4_N

VAUXP[2]

AC33

J4-60

HDR2_60_SM_4_P

VAUXN[3]

AB32

J4-54

HDR2_54_SM_13_N

VAUXP[3]

AC32

J4-56

HDR2_56_SM_13_P

VAUXN[4]

AD34

J4-50

HDR2_50_SM_5_N

VAUXP[4]

AC34

J4-52

HDR2_52_SM_5_P

electronic components distributor