ML505/ML506/ML507 Getting Started Tutorial

13

UG348 (v3.0.2) October 9, 2008

Board Setup

R

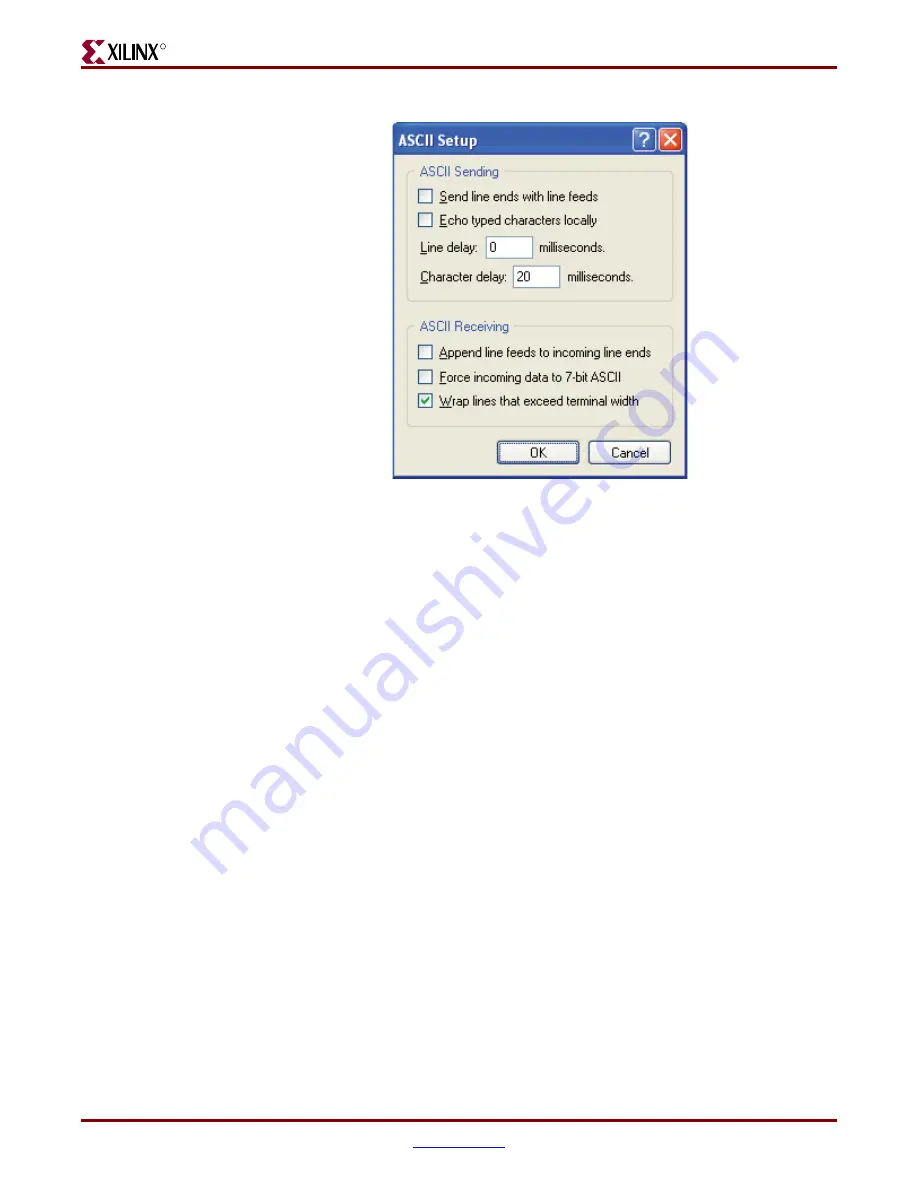

9.

For Character delay, enter 20.

10. Click

OK

→

OK

to accept the settings.

11. Connect the DVI monitor or the VGA monitor with DVI-to-VGA adapter to the board,

if available.

12. Turn on the ML50

x

board’s main power switch and press the SYSACE RESET button.

After the FPGA has been programmed, the LEDs in the lower left corner should be:

♦

Bus Error 1 and 2 = off

♦

FPGA INIT = green

♦

FPGA DONE = green

♦

System ACE “Err” = off

♦

System ACE “Stat” = green

Note:

When the CF card is ejected or not installed, the System ACE “Err” LED blinks.

13. Extract the associated training lab files to your local computer.

Unzip the training lab files to a working directory, name the directory, and make note

of the directory’s name. This directory with the extracted files is referred to as

<

LAB_DIR

> in this tutorial.

Figure 5:

ASCII Setup

UG

3

4

8

_05_04040

8

www.BDTIC.com/XILINX