MutliLINX

™

Cable

Hardware User Guide

2-7

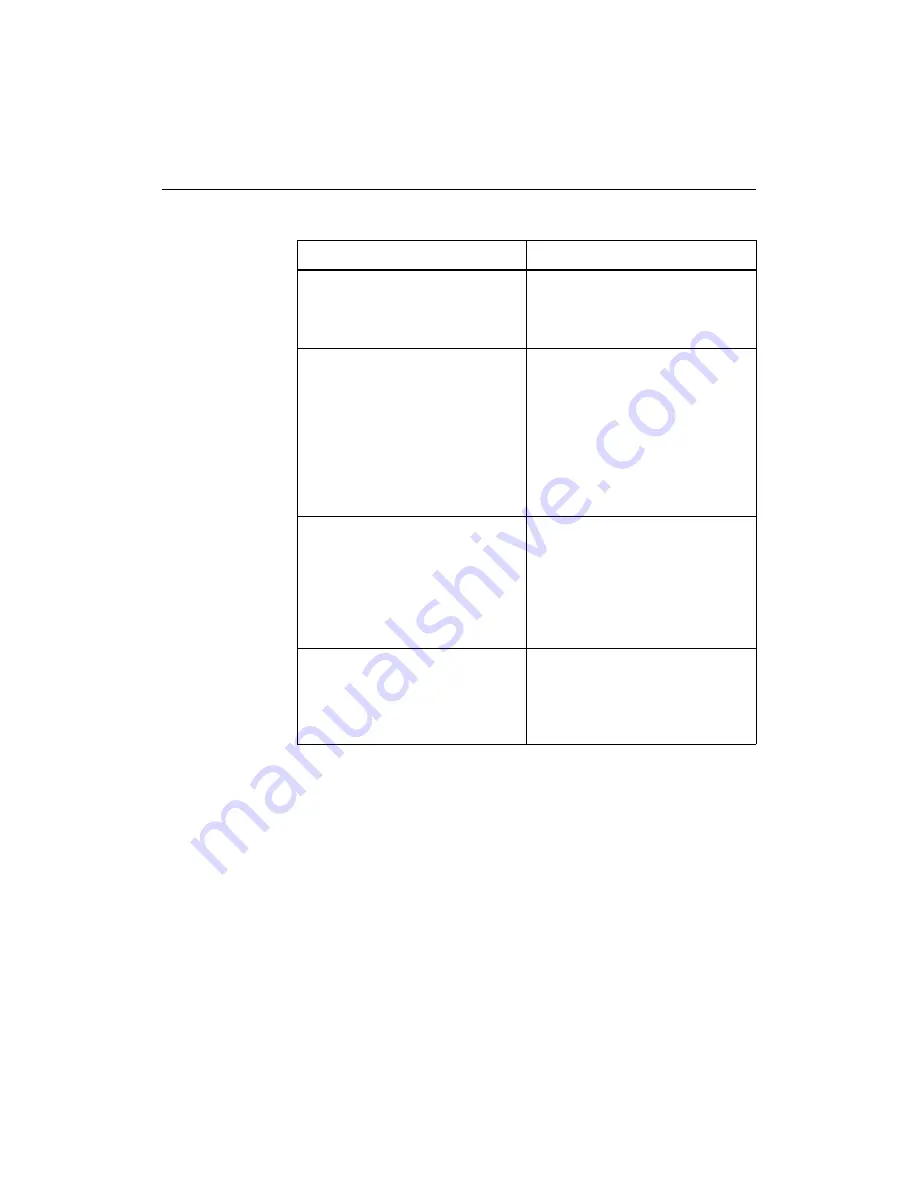

CS2

Chip Select — The CS2 pin repre-

sents Chip Select to the XC3000

FPGA while using the Peripheral

configuration mode.

CLK2-IN

Clock Input — Transmits your

system clock to the MultiLINX

electronics.

Clock must be between 120 kHz

and 10 MHz.

Connect this pin to target system

clock to synchronize the read-

back trigger with target system

clock.

CLK2-OUT

Clock Output — Drives target

system clock.

Clock can come from either the

CLK2-IN pin, or it can be inter-

nally generated by the Multi-

LINX Cable when CLK2-IN is

unconnected

WS

Write Select — The WS pin repre-

sents Write Select control for the

Asynchronous Peripheral config-

uration mode on XC4000 and

XC5200 FPGAs.

Table 2-2 MultiLINX Pin Descriptions

Signal Name

Function