Hardware User Guide

2-24

Xilinx Development System

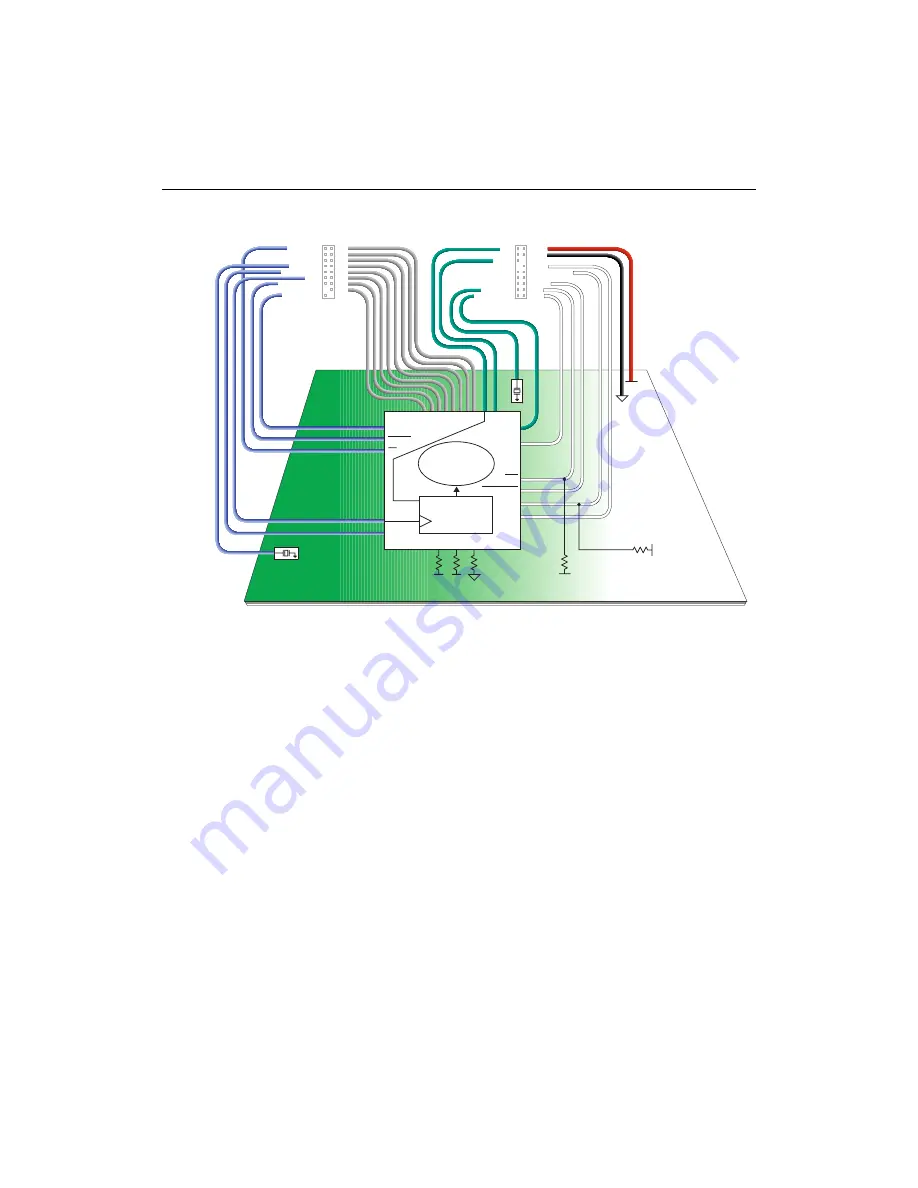

Figure 2-16 SelectMAP Mode (Virtex)

JTAG Mode

In JTAG mode Synchronous Probing is not available.

D0

D1

D2

D3

D4

D5

D6

D7

RDY/BUSY

CS2

CS1

CS0 (CS)

WS

GND

CCLK

DIN

RT

TDI

TCK

TMS

RST

TRIG

RD (TDO)

PWR

Vcco

RS (RDWR)

CLK2-IN

CLK2-OUT

CLK1-IN

CLK1-OUT

DONE (D / P)

PROG

INIT

4

2

3

1

NOTE: Pull-up resistors are 4.7k ohm.

Circuit Board

XILINX device

MultiLINX Connectors

VCC

VCC

Vcco

Vcco

(optional)

System Clock (x)

User I/O:

TRIGGER

User I/O

System Clock (y)

(optional)

M0

M1

M2

CCLK

CS

DONE

PROGRAM

INIT

D7

D6

D5

D3

D4

D2

D1

D0

WRITE

BUSY/DOUT

GCK (x)

GCK (y)

User Logic

flip-flops & latches,

LUTRAMS,

& block RAMS

Capture Control

Logic

CAPTURE

CAPCLK

User I/O

X8930

(optional)