Hardware User Guide

3-18

Xilinx Development System

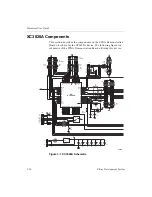

XC3020A Components

This section describes the components on the FPGA Demonstration

Board which are for the XC3020A device. The following figure is a

schematic of the FPGA Demonstration Board utilizing this device.

Figure 3-7 XC3020A Schematic

4

1

3

6

1

1

5

1

2

1

2

1K

2

4

6

10

12

14

16

18

J1B

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

LD101VR

7

8

5

6

3

4

1

2

560

8

7

3

6

4

2

1

9

1

0

5

U6

HPSP5551

1

2

560

1

2

560

3

4

5

6

7

8

3

4

5

6

7

8

5

6

3

4

7

8

1

2

560

1

2

3

J3

5

6

3

4

1

6

4.7K

1

4

1

5

+5

1

1

6

3

1

4

4

1

3

2

1

5

6

1

1

7

1

0

8

9

5

1

2

7

8

PWRDN

10

I/O

11

I/O

12

I/O

13

I/O

14

I/O

15

I/O

16

I/O

17

I/O

19

I/O

20

I/O

21

I/O

22

I/O

23

I/O

24

M1/RD

25

M0/RT

26

RESET

44

D/P

45

I/O

46

XTL1

47

I/O

48

I/O

49

I/O

50

I/O

51

I/O

53

I/O

54

I/O

55

I/O

56

I/O

57

DIN

58

DOUT

59

CCLK

60

U4

XC3020A

INP3

5

6

3

4

1

2

1K

7

8

5

6

3

4

1

2

1K

1

2

4.7K

1

4

1

3

1

5

1

6

1

7

1

8

1

9

CUT

R2

100K

1

3

R1

100K

1

3

9

11

13

15

17

7

J1A

+5

1

2

J5

R7

27K

8

9

DOUT

7

10

MCLK

2

15

MPE

DATA

1

CEO

6

CE

4

CLK

2

OE/R

3

U1

1765

3

14

SPE

OPTION

C6

0.1uF

C5

+5

0.1uF

R6

100K

1

16

PWR

1

2

J12

1

2

J9

VIN

1

VOUT

3

+5

U3

5VREG

C3

0.1uF

C2

10uF

25V

C1

0.1uF

C4

0.1uF

C7

0.1uF

C8

0.1uF

C9

0.1uF

RN10

RN11

RN17

RN16

D8

D1

SW1

+5

+5

+5

RN1

RN4

TDI

TCK

TMS

CLKI

TRIG

RD

RT

CLKO

VCC

GND

CCLK

DONE

PROG

INIT

RST

DIN

SW3

RN3

RN7

RN6

RN5

SW1

SW2

27K

M2

HDC

I/O

LDC

I/O

I/O

I/O

INIT

I/O

I/O

I/O

I/O

I/O

I/O

I/O

61

62

63

64

65

66

67

68

2

3

4

5

6

7

8

9

0I/O

1I/O

2I/O

3I/O

4I/O

5I/O

6I/O

7I/O

8I/O

9I/O

10I/O

11I/O

12I/O

13I/O

14I/O

15I/O

43

42

41

40

39

38

37

36

34

33

32

31

30

29

28

27

XTL2

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

X9242