Hardware User Guide

3-30

Xilinx Development System

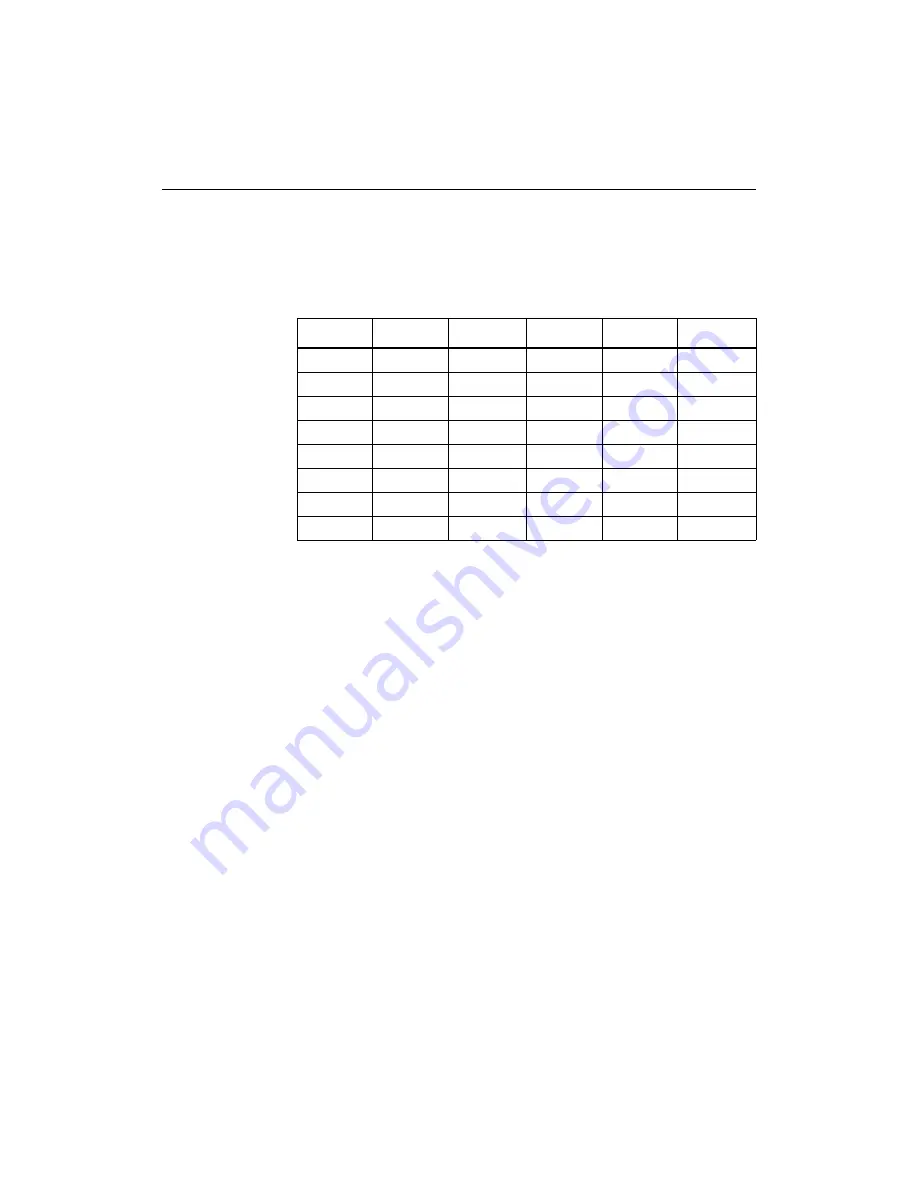

The following table lists the names and positions of the SW1 and SW2

switches for configuring the XC3020A and XC4003E FPGAs in a

daisy-chain from the serial PROM (multiple program).

Demonstration Board Operation

This section describes how to use the XChecker download cable with

the FPGA Demonstration Board and Hardware Debugger software

for device configuration. Explicit cable connection information is

included in the “Cable Hardware” chapter.

The information in this section applies to both the XC3020A and the

XC4003E devices. However, for clarity references are only made to

the XC4003E FPGA.

Note

The Parallel Cable III can also be used for FPGA configuration.

For Parallel Cable III connection information, refer to the “External

Power for the MultiLINX Cable” section of the “Cable Hardware”

chapter.

Demonstration Designs

Demonstration designs are supplied with Xilinx Foundation™ and

Alliance™ Series software. You can view or edit the demonstration

designs. Before editing, you must compile the input files with your

design implementation software.

Table 3-16 Configuring the XC3020A and XC4003E in a Daisy

Chain from the Serial PROM (Multiple Program)

Switch

Name

Position

Switch

Name

Position

SW1–1

INP

X

SW2–1

PWR

X

SW1–2

MPE

OFF

SW2–2

MPE

ON

SW1–3

SPE

OFF

SW2–3

SPE

OFF

SW1–4

M0

ON

SW2–4

M0

OFF

SW1–5

M1

ON

SW2–5

M1

OFF

SW1–6

M2

ON

SW2–6

M2

OFF

SW1–7

MCLK

ON

SW2–7

RST

X

SW1–8

DOUT

ON

SW2–8

INIT

ON

X indicates don‘t care