10

SP305 Spartan-3 Development Platform User Guide

www.xilinx.com

UG216 (v1.1) March 3, 2006

SP305 Spartan-3 Development Platform User Guide

R

User LEDs (7)

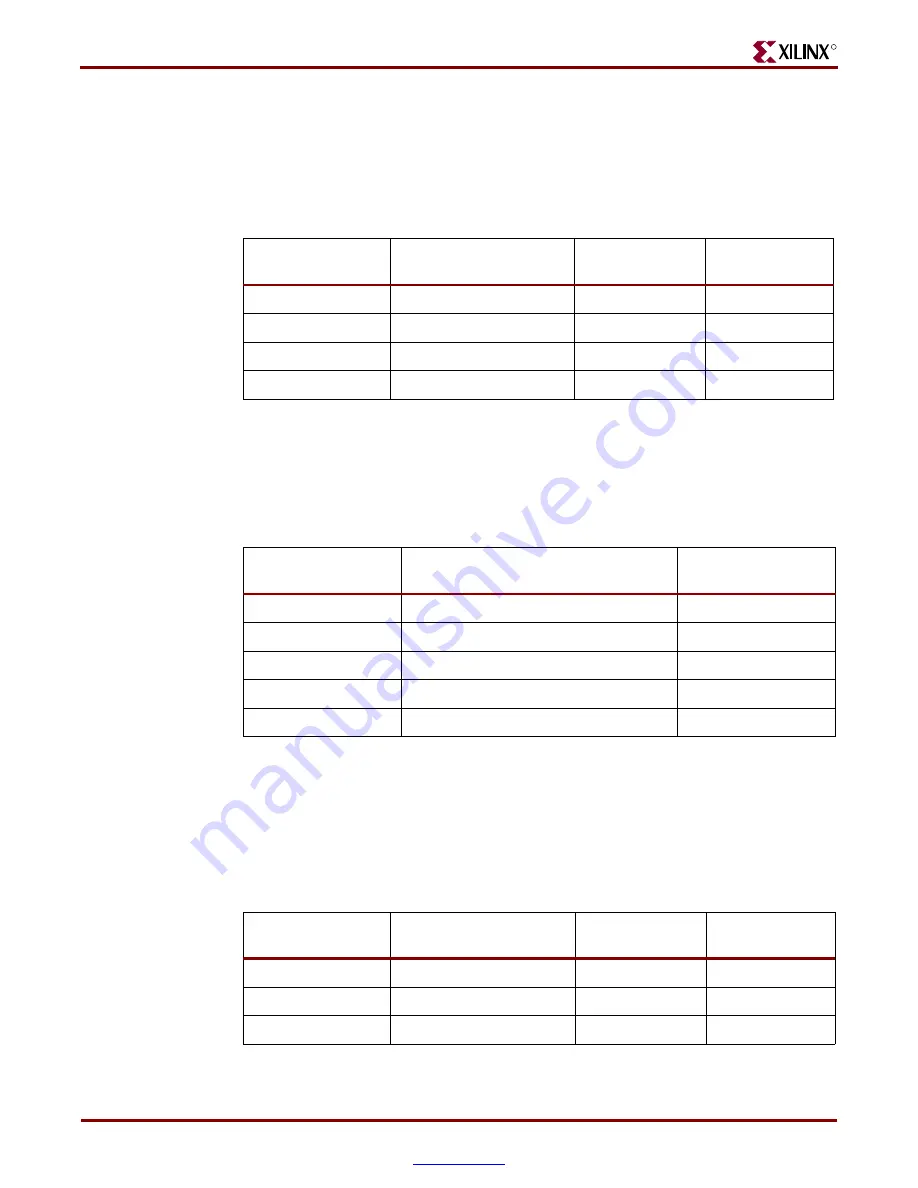

There are 4 green LEDs are general purpose LEDs arranged in a row. The LEDs are active

high LEDs directly controllable by the FPGA:

Table 2-4

summarizes the LED definitions and connections

Reference

Designator

Label/Definition

Color

FPGA Pin

GPIO LED 0

GPIO LED 1

GPIO LED 2

GPIO LED 3

.

User Push Buttons (

8

)

There are five active-high user push buttons available for general purpose usage and are

arranged in a

North-East-South-West-Center

orientation (only the

West

one is cited in

Figure 2-2, page 6

). The user push button connections are summarized in

Table 2-5

.

Reference

Designator

Label/Definition

FPGA Pin

GPIO Switch North

GPIO Switch South

GPIO Switch East

GPIO Switch West

GPIO Switch Center

User Push Button LEDs (9)

There are 5 green LEDs positioned next to the

North-East-South-West-Center

oriented

push buttons (only the

Center

one is called out in

Figure 2-2, page 6

). The LEDs are active

high and are directly controllable by the FPGA:

Table 2-6

summarizes the LED definitions and connections.

Table 2-4:

User LED Connections

DS15

Green

J3

DS4

Green

J4

DS5

Green

D22

DS6

Green

E22

Table 2-5:

User Push Button Connections

SW3

H6

SW4

F3

SW5

G6

SW7

G4

SW6

F1

Table 2-6:

User LED Connections

Reference

Designator

Label/Definition

Color

FPGA Pin

DS14

LED North

Green

K6

DS3

LED South

Green

G5

DS11

LED East

Green

F4