VC707 Evaluation Board

79

UG885 (v1.2) February 1, 2013

Appendix B

VITA 57.1 FMC Connector Pinouts

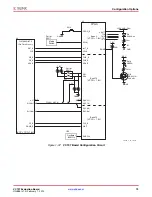

shows the pinout of the FMC1 HPC connector J35. For more information, see

VITA 57.1 FMC1 HPC Connector (Partially Populated), page 54

.

X-Ref Target - Figure B-1

Figure B-1:

FMC1 HPC Connector Pinout

UG885_aC_01_020612

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

VREF_B_M2C

GND

GND

CLK2_M2C_P

CLK2_M2C_N

GND

HA02_P

HA02_N

GND

HA06_P

HA06_N

GND

HA10_P

HA10_N

GND

HA17_P_CC

HA17_N_CC

GND

HA21_P

HA21_N

GND

HA23_P

HA23_N

GND

HB00_P_CC

HB00_N_CC

GND

HB06_P_CC

HB06_N_CC

GND

HB10_P

HB10_N

GND

HB14_P

HB14_N

GND

HB17_P_CC

HB17_N_CC

GND

VIO_B_M2C

GND

CLK3_M2C_P

CLK3_M2C_N

GND

GND

HA03_P

HA03_N

GND

HA07_P

HA07_N

GND

HA11_P

HA11_N

GND

HA14_P

HA14_N

GND

HA18_P

HA18_N

GND

HA22_P

HA22_N

GND

HB01_P

HB01_N

GND

HB07_P

HB07_N

GND

HB11_P

HB11_N

GND

HB15_P

HB15_N

GND

HB18_P

HB18_N

GND

VIO_B_M2C

GND

VREF_A_M2C

PRSNT_M2C_L

GND

CLK0_M2C_P

CLK0_M2C_N

GND

LA02_P

LA02_N

GND

LA04_P

LA04_N

GND

LA07_P

LA07_N

GND

LA11_P

LA11_N

GND

LA15_P

LA15_N

GND

LA19_P

LA19_N

GND

LA21_P

LA21_N

GND

LA24_P

LA24_N

GND

LA28_P

LA28_N

GND

LA30_P

LA30_N

GND

LA32_P

LA32_N

GND

VADJ

GND

DP1_M2C_P

DP1_M2C_N

GND

GND

DP2_M2C_P

DP2_M2C_N

GND

GND

DP3_M2C_P

DP3_M2C_N

GND

GND

DP4_M2C_P

DP4_M2C_N

GND

GND

DP5_M2C_P

DP5_M2C_N

GND

GND

DP1_C2M_P

DP1_C2M_N

GND

GND

DP2_C2M_P

DP2_C2M_N

GND

GND

DP3_C2M_P

DP3_C2M_N

GND

GND

DP4_C2M_P

DP4_C2M_N

GND

GND

DP5_C2M_P

DP5_C2M_N

GND

RES1

GND

GND

DP9_M2C_P

DP9_M2C_N

GND

GND

DP8_M2C_P

DP8_M2C_N

GND

GND

DP7_M2C_P

DP7_M2C_N

GND

GND

DP6_M2C_P

DP6_M2C_N

GND

GND

GBTCLK1_M2C_P

GBTCLK1_M2C_N

GND

GND

DP9_C2M_P

DP9_C2M_N

GND

GND

DP8_C2M_P

DP8_C2M_N

GND

GND

DP7_C2M_P

DP7_C2M_N

GND

GND

DP6_C2M_P

DP6_C2M_N

GND

GND

RES0

GND

DP0_C2M_P

DP0_C2M_N

GND

GND

DP0_M2C_P

DP0_M2C_N

GND

GND

LA06_P

LA06_N

GND

GND

LA10_P

LA10_N

GND

GND

LA14_P

LA14_N

GND

GND

LA18_P_CC

LA18_N_CC

GND

GND

LA27_P

LA27_N

GND

GND

SCL

SDA

GND

GND

GA0

12P0V

GND

12P0V

GND

3P3V

GND

PG_C2M

GND

GND

GBTCLK0_M2C_P

GBTCLK0_M2C_N

GND

GND

LA01_P_CC

LA01_N_CC

GND

LA05_P

LA05_N

GND

LA09_P

LA09_N

GND

LA13_P

LA13_N

GND

LA17_P_CC

LA17_N_CC

GND

LA23_P

LA23_N

GND

LA26_P

LA26_N

GND

TCK

TDI

TDO

3P3VAUX

TMS

TRST_L

GA1

3P3V

GND

3P3V

GND

3P3V

GND

HA01_P_CC

HA01_N_CC

GND

GND

HA05_P

HA05_N

GND

HA09_P

HA09_N

GND

HA13_P

HA13_N

GND

HA16_P

HA16_N

GND

HA20_P

HA20_N

GND

HB03_P

HB03_N

GND

HB05_P

HB05_N

GND

HB09_P

HB09_N

GND

HB13_P

HB13_N

GND

HB19_P

HB19_N

GND

HB21_P

HB21_N

GND

VADJ

GND

PG_M2C

GND

GND

HA00_P_CC

HA00_N_CC

GND

HA04_P

HA04_N

GND

HA08_P

HA08_N

GND

HA12_P

HA12_N

GND

HA15_P

HA15_N

GND

HA19_P

HA19_N

GND

HB02_P

HB02_N

GND

HB04_P

HB04_N

GND

HB08_P

HB08_N

GND

HB12_P

HB12_N

GND

HB16_P

HB16_N

GND

HB20_P

HB20_N

GND

VADJ

GND

CLK1_M2C_P

CLK1_M2C_N

GND

GND

LA00_P_CC

LA00_N_CC

GND

LA03_P

LA03_N

GND

LA08_P

LA08_N

GND

LA12_P

LA12_N

GND

LA16_P

LA16_N

GND

LA20_P

LA20_N

GND

LA22_P

LA22_N

GND

LA25_P

LA25_N

GND

LA29_P

LA29_N

GND

LA31_P

LA31_N

GND

LA33_P

LA33_N

GND

VADJ

GND

K

J

H

G

F

E

D

C

B

A