32

Virtex-6 FPGA Connectivity Kit Getting Started

UG664 (v1.4) July 6, 2011

Getting Started with the Connectivity Targeted Reference Design Demo

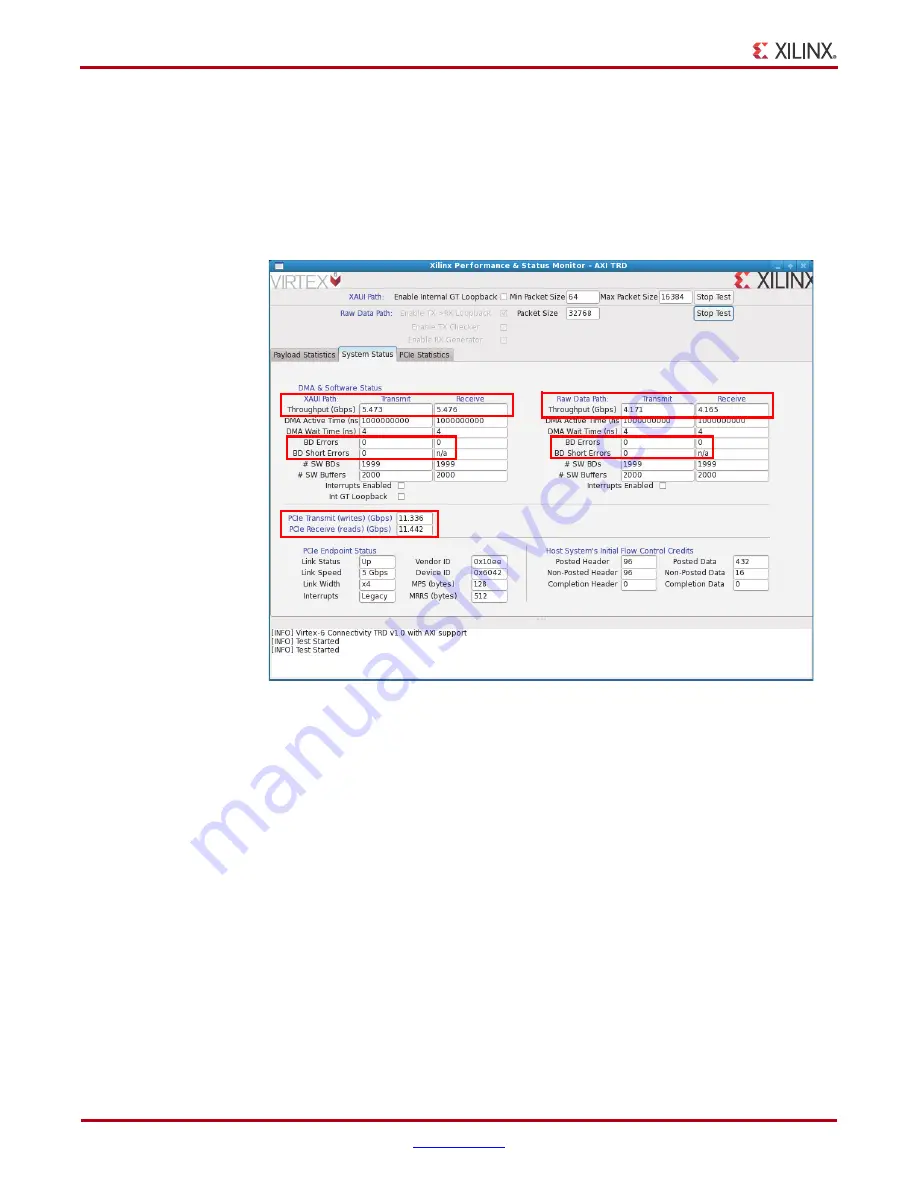

18. Performance Monitor Application: In the dialog box shown in

, verify data

throughput and error-free operation:

a.

Verify the PCIe throughput is approximately 10 Gbps.

b. Verify the DMA channel throughput for the XAUI path and DMA channel

throughput for the Raw Data path together is approximately 9 Gbps.

c.

Verify there are no buffer descriptor errors for error-free operation.

Congratulations! The Virtex-6 FPGA Connectivity Kit is now set up. The pre-built

connectivity targeted reference design demonstration has been tested, using the built-in

block for PCI Express (4-lane 5 GT/s configuration for PCI Express, v2.0), XAUI

LogiCORE IP module, a Virtual FIFO memory controller that interfaces to the onboard

DDR3 SODIMM device, and a third-party DMA controller for PCI Express.

X-Ref Target - Figure 24

Figure 24:

Verify Error-Free Operation in the Performance Monitor

UG664_10_0

9

0

8

10

Summary of Contents for Virtex-6 FPGA

Page 1: ...Virtex 6 FPGA Connectivity Kit Getting Started Guide UG664 v1 4 July 6 2011 XPN 0402826 03...

Page 4: ...Virtex 6 FPGA Connectivity Kit Getting Started www xilinx com UG664 v1 4 July 6 2011...

Page 6: ...6 www xilinx com Virtex 6 FPGA Connectivity Kit Getting Started UG664 v1 4 July 6 2011...