Virtex-6 FPGA Connectivity Kit Getting Started

69

UG664 (v1.4) July 6, 2011

Getting Started with the Virtex-6 FPGA IBERT Reference Design

6.

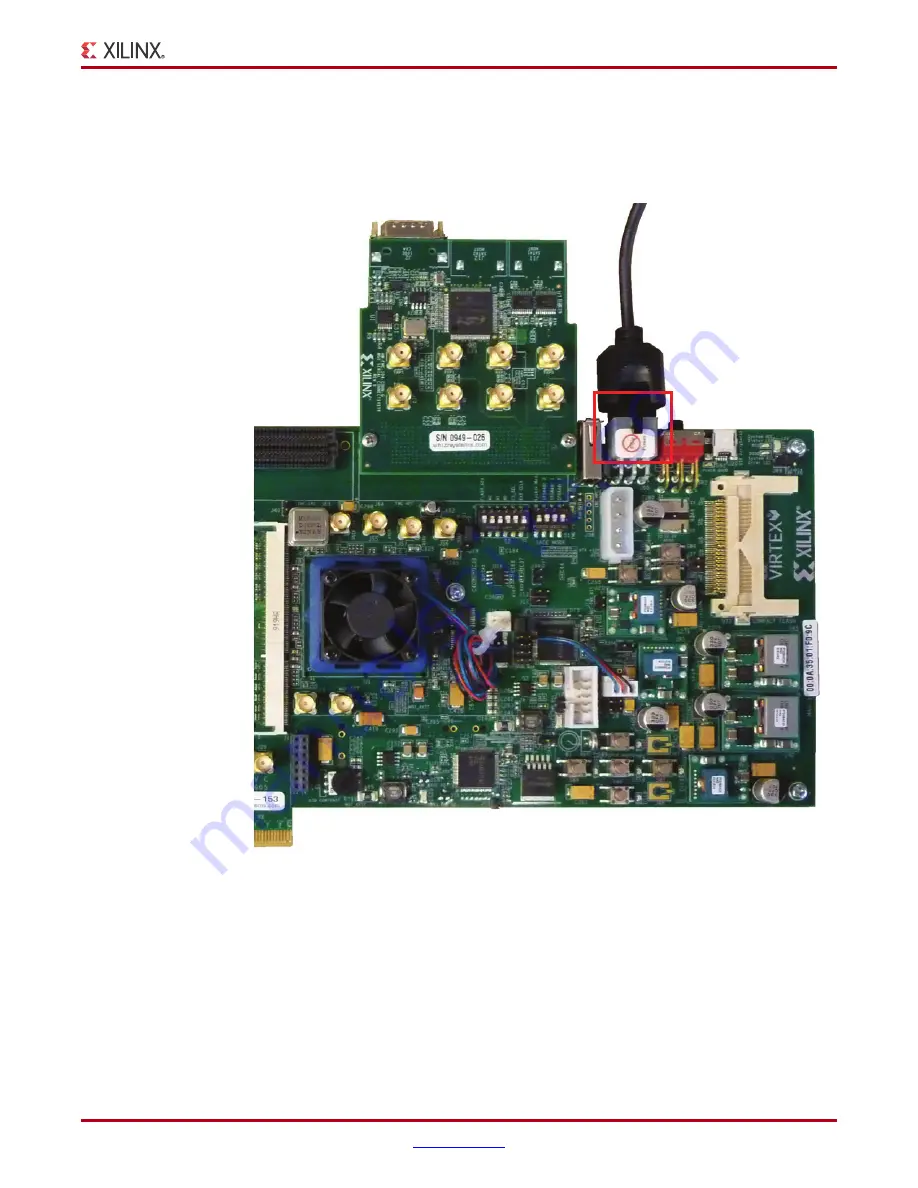

Board Setup V – Connect the power connector:

a.

Using the included power supply, connect the power supply connector to the

ML605 board as shown in

.

b. The power switch SW2 should be switched to the ON position

.

X-Ref Target - Figure 70

Figure 70:

Powering Up the ML605 Board

UG664_47_011710

Summary of Contents for Virtex-6 FPGA

Page 1: ...Virtex 6 FPGA Connectivity Kit Getting Started Guide UG664 v1 4 July 6 2011 XPN 0402826 03...

Page 4: ...Virtex 6 FPGA Connectivity Kit Getting Started www xilinx com UG664 v1 4 July 6 2011...

Page 6: ...6 www xilinx com Virtex 6 FPGA Connectivity Kit Getting Started UG664 v1 4 July 6 2011...