28

Virtex-6 FPGA System Monitor

UG370 (v1.1) June 14, 2010

System Monitor Control Logic

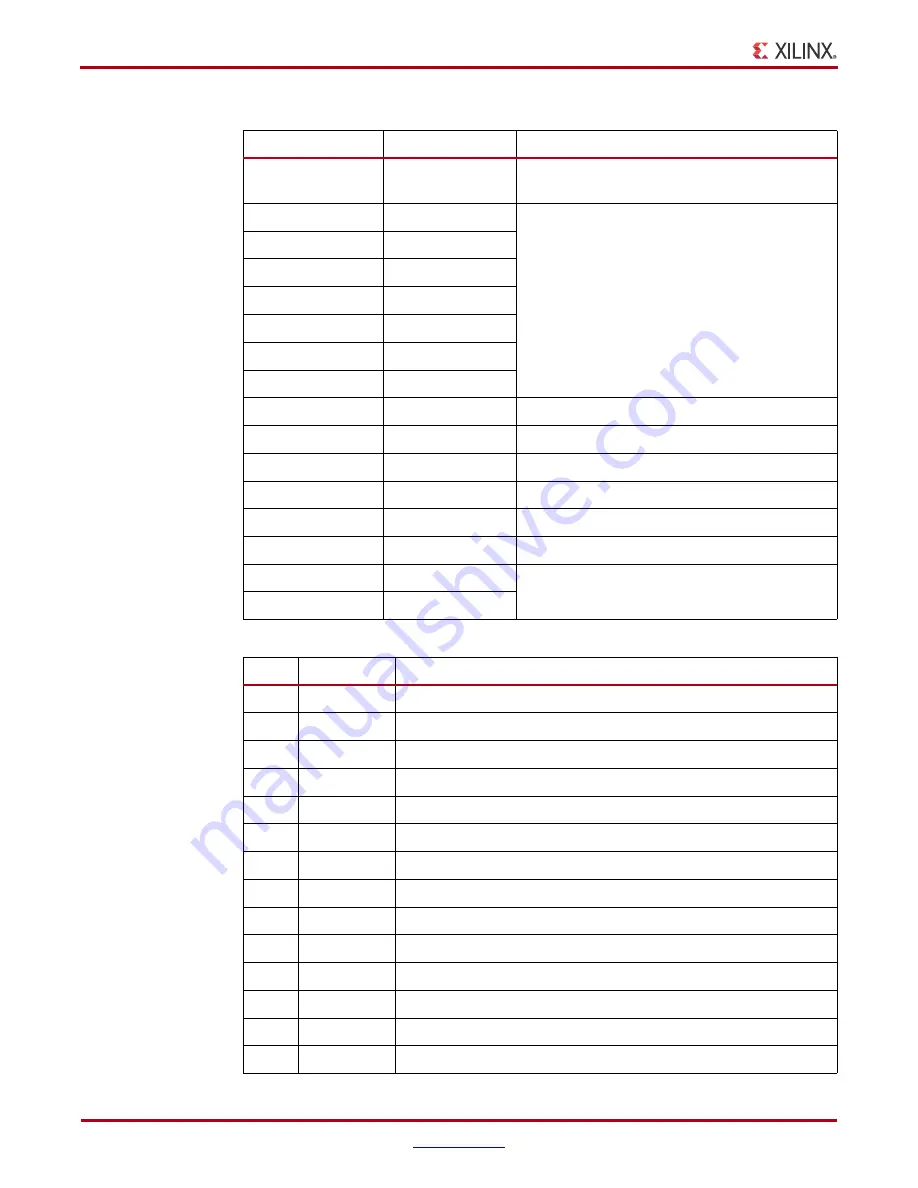

Table 15:

Sequencer ADC Channel Averaging, Control Register

4Ah

Bit

ADC Channel

Description

0

8

Averaging for the calibration coefficients is

enabled using CAVG in Configuration Register 0.

1

9

Invalid channel selection

2

10

3

11

4

12

5

13

6

14

7

15

8

0

Enable averaging—On

-Chip temperature

9

1

Enable averaging—On

-Chip V

CCINT

sensor

10

2

Enable averaging—On

-Chip V

CCAUX

sensor

11

3

Enable averaging—V

P

, V

N

12

4

Enable averaging—V

REFP

(1.25V)

13

5

Enable averaging—V

REFN

(0V)

14

6

Invalid channel selection

15

7

Table 16:

Sequencer ADC Channel Averaging, Control Register

4Bh

Bit

ADC Channel

Description

0

16

Enable averaging—VAUXP[0],VAUXN[0]—Auxiliary channel 1

1

17

Enable averaging—VAUXP[1],VAUXN[1]—Auxiliary channel 2

2

18

Enable averaging—VAUXP[2],VAUXN[2]—Auxiliary channel 3

3

19

Enable averaging—VAUXP[3],VAUXN[3]—Auxiliary channel 4

4

20

Enable averaging—VAUXP[4],VAUXN[4]—Auxiliary channel 5

5

21

Enable averaging—VAUXP[5],VAUXN[5]—Auxiliary channel 6

6

22

Enable averaging—VAUXP[6],VAUXN[6]—Auxiliary channel 7

7

23

Enable averaging—VAUXP[7],VAUXN[7]—Auxiliary channel 8

8

24

Enable averaging—VAUXP[8],VAUXN[8]—Auxiliary channel 9

9

25

Enable averaging—VAUXP[9],VAUXN[9]—Auxiliary channel 10

10

26

Enable averaging—VAUXP[10],VAUXN[10]—Auxiliary channel 11

11

27

Enable averaging—VAUXP[11],VAUXN[11]—Auxiliary channel 12

12

28

Enable averaging—VAUXP[12],VAUXN[12]—Auxiliary channel 13

13

29

Enable averaging—VAUXP[13],VAUXN[13]—Auxiliary channel 14

www.BDTIC.com/XILINX