32

www.xilinx.com

Spartan-3A DSP 3400A Edition User Guide

UG498 (v2.2) November 17, 2008

Chapter 1:

Introduction

R

♦

Provide PWM control of the fan speed

♦

Provide fan tachometer readings

♦

Generate interrupts/alarms based on readings

Connector P3 is a keyed three-pin fan header similar to the ones in computers. It is

designed to support a 5V DC fan. To bypass the fan controller device and operate the

fan at full speed, you can use connector JP9.

Under high-power operating conditions, a heat sink and/or fan for the FPGA can be

accommodated on the board (for example, Calgreg Electronics Smart-CLIP family of

heat sink/fan assemblies). The Spartan-3A DSP 3400A Edition board does not come

with a heat sink and/or fan.

23.

Program and Reset Buttons

Button S10 forces the FPGA to be reprogrammed; button S9 forces the System ACE to

reset.

24.

FPGA

XC3SD3400A-4FGG676C Xilinx Spartan-3A DSP FPGA. The board supports

configuration in several modes: JTAG, master serial, slave serial, master SelectMAP,

slave SelectMAP, byte-wide peripheral interface (BPI) up, BPI down, and SPI modes

See

Chapter 2, “Configuration Options.”

The FPGA is also equipped with four I/O banks.

Table 1-17

defines the I/O voltage

applied to each bank.

25.

JTAG Header

The JTAG header (P5) allows programming devices and troubleshooting the FPGA.

The JTAG port supports the Xilinx Parallel Cable III, Parallel Cable IV, or Platform USB

cable products. (Third-party configuration products may also be available.) The JTAG

chain can also be extended to the FMC expansion module when it is present. See

Chapter 2, “Configuration Options.”

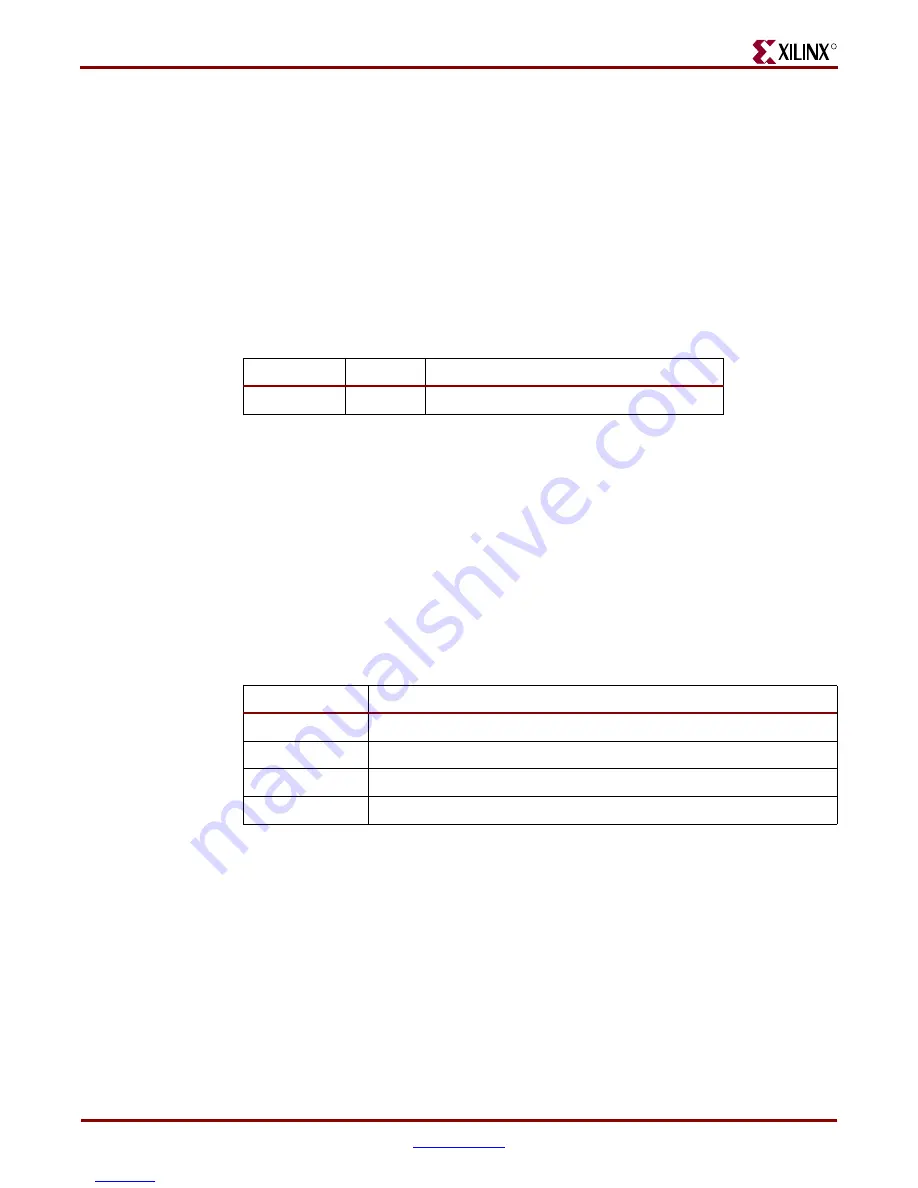

Table 1-16:

FPGA Fan Controller Interface

Signal

FPGA Pin

Description

FAN_ALERT

T17

Interrupt to signal out-of-limit conditions.

Table 1-17:

FPGA I/O Bank Voltage Rail

FPGA Bank

I/O Voltage Rail

0

FMC expansion connector #2 adjustable (1.5V, 1.8V, 2.5V, or 3.3V)

1

1.8V

2

3.3V

3

FMC expansion connector #1 adjustable (1.5V, 1.8V, 2.5V, or 3.3V)

electronic components distributor