9

Circuit Description

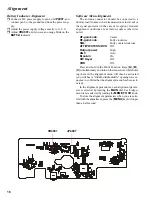

ALC Circuit

The output from the directional coupler is routed from

connector J3002 and applied to the ALC circuit via con-

nector J1001 on the MAIN Unit.

The ALC circuit consists of an op-amp circuit for am-

plifying the forward and reflected voltage, a time-constant

ALC amplifier, and a transmit signal control circuit on

the MAIN Unit. The forward voltage from connector

J1001 on the MAIN Unit is added with a DC control volt-

age and is then applied to op-amp IC Q1111 (

NJM2902V

).

The reflected voltage is added with a DC control voltage

and is then applied to op-amp IC Q1112 (

NJM2904V

).

In the event of high SWR conditions (SWR 3:1 or more),

transmitter output is reduced, thus protecting the PA Unit

from potential damage; a “HI SWR” indication also ap-

pears on the LCD, alerting the user to an antenna prob-

lem.

The ALC amplifier magnifies the forward wave out-

put via transistor Q1009 (

2SC4154

). This output then

passes through a fast-attack, slow-delay RC time-constant

circuit, which consists of R1051 and C1051, for input to

the TX signal control circuit on the MAIN Unit. The TX

control circuit adjusts the IF amplifier gain via gate 2 of

FET Q1061 (

BB304CDW

) of the 2nd IF amplifier cir-

cuit, to prevent the TX output from exceeding the preset

level.

PLL Frequency Synthesizer

The PLL Frequency Synthesizer consists mainly of the

master reference oscillator circuit, 2nd local oscillator cir-

cuit, PLL IC, and CAR-DDS and REF-DDS units, which

digitally synthesize carrier outputs, plus a PLL circuit

which contains a voltage controlled oscillator (VCO).

Master Reference Oscillator Circuit

The master reference oscillator uses a Crystal Oscilla-

tor (oscillation frequency: 22.625 MHz) composed of

Q5001 (

2SC4400-4

), X5001, TC5001, C5001, and

R5005. The reference oscillator signal passes through a

buffer amplifier Q5002 (

2SC4400-4

), and is then fed to

the MAIN Unit via J5002.

CAR-DDS Circuit REF-DDS Circuit

DDS ICs Q1062 (

AD9835BRU

), and Q2016

(

AD9850BAS

) each contain a shift register, selector,

phase accumulator, and ROM. The reference oscillation

frequency (22.625 MHz) that is delivered to each of the

DDS Units is applied to each DDS IC after amplification

by transistors Q1043, Q1046, Q1048, and Q1059 (all

2SC4400-3

).

The DDS outputs contain digital amplitude data cor-

responding to serial frequency data from CPU IC Q1049.

The DDS frequency range is 453.5 ~ 466.5 kHz (center

frequency = 455.0 kHz) for the CAR-DDS, and 7.2-8.0

MHz for the REF DDS.

1st Local Oscillator Circuit

VCO output is buffer-amplified by Q2011 (

2SC5374

)

and Q2022 (

UPC2713T

), and passes through a low-pass

filter. It is then fed to the TX/RX frequency mixer circuit-

ry of the MAIN Unit.

2nd Local Oscillator Circuit

The 2nd LO circuit is a Hartley-type overtone oscilla-

tor circuit (frequency: 67.875 MHz) composed of Q1052

(

2SC4400-3

) on the MAIN Unit.

PLL Circuit

The PLL circuit is a frequency mixing type composed

of a VCO, mixer, PLL IC, and loop filter. The VCO con-

sists of five circuits (VCO1, VCO2, VCO3, VCO4 and

VCO5), with a frequency range of 68.430-538.330 MHz

divided into five bands, allocated to the five VCO cir-

cuits. VCO1-VCO5 consist mainly of FETs Q2004,

Q2005, and Q2006 (all 2

SK210GR

); transistors Q2009

and Q2010 (both

2SC5374

); diodes D2001-D2006 (all

HVC362

), D2007 (

1SV282

), D2008 (

1SV281

), and

D2009 (

1SV286

); and coils T2001-T2003, L2010, and

L2011.

The VCO switching signal from the connector J2002

is used to drive switching transistors Q2001, Q2002,

Q2003, Q2012, and Q2013 (all

DTC124EU

) to switch

the source terminal of the oscillator FET.

The 68.430-538.330 MHz VCO signal is buffer-am-

plified by Q2023 (

UPC1688G

), and fed to PLL IC Q2021

(

FQ7925

.)

The REF-DDS signal (7.2-8.0 MHz) is fed to PLL IC

Q2021 after it passes through a low-pass filter composed

of C2064, C2067, C2069, C2071, C2075, L2014, L2015,

and L2016, and is fed to PLL IC Q2021 (

FQ7925

.) The

phase of the reference frequency and that of the signal

input to the PLL IC are compared, and a signal whose

pulse corresponds to the phase difference is produced.

Summary of Contents for FT-897

Page 5: ...Block Diagram 5...

Page 6: ...Block Diagram 6 Note...

Page 21: ...21 MAIN Unit Circuit Diagram...

Page 22: ...22 MAIN Unit Note...

Page 52: ...52 MAIN Unit Note...

Page 59: ...59 PA Unit Circuit Diagram...

Page 60: ...60 PA Unit Note...

Page 73: ...73 PANEL Unit Circuit Diagram...

Page 74: ...74 PANEL Unit Note...

Page 75: ...75 PANEL Unit H Parts Layout Side A 1 2 3 F A C B E D BRPG1211C D4007 4010 4012 G...