28

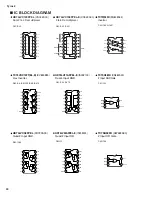

Tyros2

MO

TR

OWNE

BEDIE

MODE

PIN

NO.

I/O

FUNCTION

NAME

PIN

NO.

I/O

FUNCTION

NAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

MD1

MD2

Vcc(RTC)

XTAL2

EXTAL2

Vss(RTC)

NMI

IRQ0/IRL0/PTH0

IRQ1/IRL1/PTH1

IRQ2/IRL2/PTH2

IRQ3/IRL3/PTH3

IRQ4/PTH4

D31/PTB7

D30/PTB6

D29/PTB5

D28/PTB4

D27/PTB3

D26/PTB2

VssQ

D25/PTB1

VccQ

D24/PTB0

D23/PTA7

D22/PTA6

D21/PTA5

D20/PTA4

Vss

D19/PTA3

Vcc

D18/PTA2

D17/PTA1

D16/PTA0

VssQ

D15

VccQ

D14

D13

D12

D11

D10

D9

D8

D7

D6

VssQ

D5

VccQ

D4

D3

D2

D1

D0

A0

A1

A2

A3

VssQ

A4

VccQ

A5

A6

A7

A8

A9

A10

A11

A12

A13

VssQ

A14

VccQ

A15

A16

A17

A18

A19

A20

A21

Vss

A22

Vcc

A23

VssQ

A24

VccQ

A25

BS/PTK4

RD

WE0/DQMLL

WE1/DQMLU/WE

WE2/DQMUL/ICIORD/PTK6

WE3/DQMUU/ISIOWR/PTK7

RD/WR

AUDSYNC/PTE7

VssQ

CS0/MCS0

VccQ

CS2/PTK0

CS3/PTK1

CS4/PTK2

CS5/CE1A/PTK3

CS6/CE1B

CE2A/PTE4

CE2B/PTE5

I

I

-

O

I

-

I

I

I

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

-

I/O

-

I/O

I/O

I/O

I/O

I/O

-

I/O

-

I/O

I/O

I/O

-

I/O

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

-

I/O

-

I/O

I/O

I/O

I/O

I/O

O

O

O

O

-

O

-

O

O

O

O

O

O

O

O

O

-

O

-

O

O

O

O

O

O

O

-

O

-

O

-

O

-

O

I/O

O

O

O

I/O

I/O

O

I/O

-

O

-

I/O

I/O

I/O

I/O

O

I/O

I/O

Mode control

Power 2.0 V

Crystal oscillator

Ground

Non-maskable interrupt request

Interrupt request / Port H

Data bus / Port B

Ground

Data bus / Port B

Power 3.3 V

Data bus / Port B

Data bus / Port A

Ground

Data bus / Port A

Power 1.8 V

Data bus / Port A

Ground

Data bus

Power 3.3 V

Data bus

Ground

Data bus

Power 3.3 V

Data bus

Address bus

Ground

Address bus

Power 3.3 V

Address bus

Ground

Address bus

Power 3.3 V

Address bus

Ground

Address bus

Power 2.0 V

Address bus

Ground

Address bus

Power 3.3 V

Address bus

Bus cycle / Port K

Read strobe

Select signal (D7-D0) / D QM (SDRAM)

Select signal (D15-D8) / D QM (SDRAM) / Write enable

Select signal (D23-D16) / D QM (SDRAM) / I/O read / Port K

Select signal (D31-D24) / D QM (SDRAM) / I/O write / Port K

Read / Write

AUD cycle / Port E

Ground

Chip select / Mask ROM chip select

Power 3.3V

Chip select / Port K

Chip select / Chip enable / Port K

Chip select / Chip enable

Chip enable / Port E

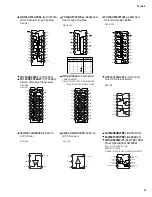

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

CKE/PTK5

RAS3L/PTJ0

PTJ1

CASL/PTJ2

VssQ

CASU/PTJ3

VccQ

PTJ4

PTJ5

DACK0/PTD5

DACK1/PTD7

PTE6

PTE3

RAS3U/PTE2

PTE1

TDO/PTE0

BACK

BREQ

WAIT

RESETM

ADTRG/PTH5

IOIS16/PTG7

ASEMD0/PTG6

ASEBRKAK/PTG5

PTG4/CKIO2

AUDATA3/PTG3

AUDATA2/PTG2

Vss

AUDATA1/PTG1

Vcc

AUDATA0/PTG0

TRST/PTF7/PINT15

TMS/PTF6/PINT14

TDI/PTF5/PINT13

TCK/PTF4/PINT12

IRLS3/PTF3/PINT11

IRL2/PTF2/PINT10

IRLS1/PTF1/PINT9

IRLS0/PTF0/PINT8

MD0

Vcc(PLL1)

CAP1

Vss(PLL1)

Vss(PLL2)

CAP2

VCC(PLL2)

AUDCK/PTH6

Vss

Vss

Vcc

XTAL

EXTAL

STATUS0/PTJ6

STATUS1/PTJ7

TCLK/PTH7

/IRQOUT

VssQ

CKIO

VccQ

TXD0/SCPT0

SCK0/SCPT1

TXD1/SCPT2

SCK1/SCPT3

TXD2/SCPT4

SCK2/SCPT5

RTS2/SCPT6

RXD0/SCPT0

RXD1/SCPT2

Vss

RXD2/SCPT4

Vcc

CTS2/IRQ5/SCPT7

MCS7/PTC7/PINT7

MCS5/PTC5/PINT5

MCS4/PTC4/PINT4

VssQ

WAKEUP/PTD3

VccQ

RESETOUT/PTD2

MCS3/PTC3/PINT3

MCS2/PTC2/PINT2

MCS1/PTC1/PINT1

MCS0/PTC0/PINT0

DRAK0/PTD1

DRAK1/PTD0

DREQ0/PTD4

DREQ1/PTD6

RESETP

CA

MD3

MD4

MD5

AVss

AN0/PTL0

AN1/PTL1

AN2/PTL2

AN3/PTL3

AN4/PTL4

AN5/PTL5

AVcc

AN6/DA1/PTL6

AN7/DA0/PTL7

AVss

I/O

I/O

I/O

I/O

-

I/O

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

I

I

I

I

I

I

I/O

I/O

I/O

I/O

-

I/O

-

I/O

I

I

I

I

I

I

I

I

I

-

-

-

-

-

-

I

-

-

-

O

I

I/O

I/O

I/O

O

-

I/O

-

O

I/O

O

I/O

O

I/O

I/O

I

I

-

I

-

I

I/O

I/O

I/O

I/O

-

I/O

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

I

I

I

I

-

I

I

I

I

I

I

-

I/O

I/O

-

CK enable / Port K

RAS address bus / Port J

Port J

CAS address bus / Port J

Ground

CAS address bus / Port J

Power 3.3 V

Port J

DMA acknowledge / Port D

Port E

RAS address bus / Port E

Port E

Test data / Port E

Bus acknowledge

Bus request

Hardware wait request

Manual reset

Analog trigger / Port H

Write protect / Port G

ASE mode / Port G

ASE break acknowledge / Port G

Port G / Clock output

AUD data / Port G

Ground

AUD data / Port G

Power 2.0 V

AUD data / Port G

Test reset / Port F / Port interruption

Test mode switch / Port F / Port interruption

Test data / Port F / Port interruption

Test clock / Port F / Port interruption

Interrupt request / Port F / Port interruption

Mode control

Power 2.0 V

Capacitor

Ground

Ground

Capacitor

Power 2.0 V

AUD clock / Port H

Ground

Power 2.0 V

Crystal oscillator

Processor status / Port J

Timer clock / Port H

Interrupt request output

Ground

System clock input / output

Power 3.3 V

Data transmission / SCI port

Serial clock / SCI port

Data transmission / SCI port

Serial clock / SCI port

Data transmission / SCI port

Serial clock / SCI port

Transmit request / SCI port

Data reception / SCI port

Ground

Data reception / SCI port

Power 2.0 V

Transmit clear / Interrupt request / SCI port

Mask ROM chip select / Port C / Port interruption

Ground

Standby mode Interrupt request output / Port D

Power 3.3 V

Reset output / Port D

Mask ROM chip select / Port C / Port interruption

DMA acknowledge / Port D

DMA request / Port D

Power on reset

Chip active

Mode control

Analog ground

Analog input / Port L

Analog power 3.3 V

Analog input / Analog output / Port L

Analog ground

HD6417709SHF200BV

(X2687B00)

CPU

(SH3)

MCS6/PTC6/PINT6