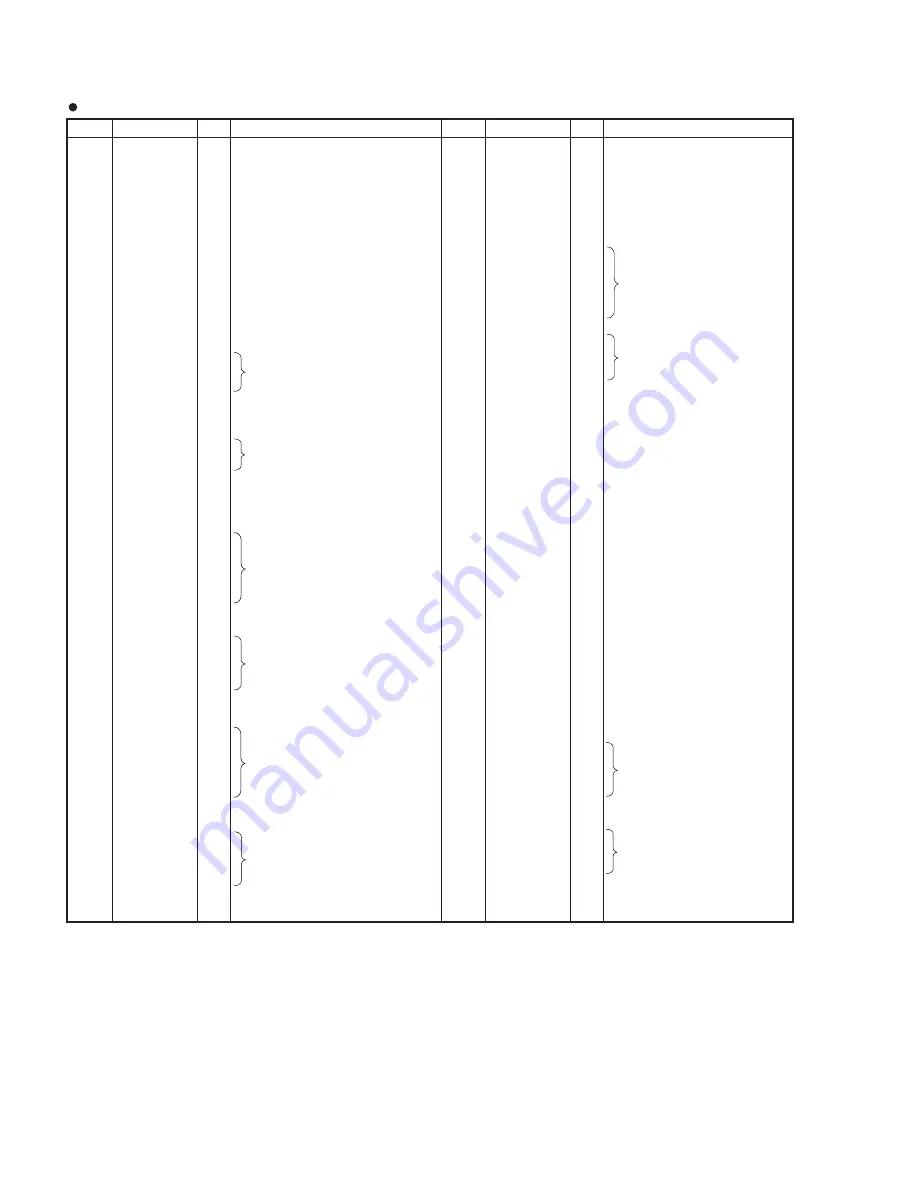

32

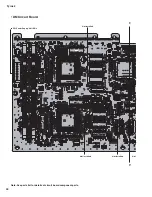

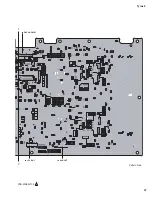

Tyros2

MO

TR

OWNE

BEDIE

MODE

PinNo.

NAME

I/O

FUNCTION/CONNECTION

PinNo.

NAME

I/O

FUNCTION/CONNECTION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

GND

TDI

DGA_AUDIO_IN

I/O

DGA_OUT

I/O

GND

I/O

IDERD_O

IDEWR_O

IDEMACK_O

CLOCK_INPUT

VCCO

DMACLR

I/O

I/O

I/O

GND

HDIRQ

XHDIRQ

I/O

I/O

FS64DGA

TCK

VCC

GND

I

I/O

I/O

I/O

I/O

GND

VCCO

I/O

I/O

I/O

I/O

CK512

FS128

I/O

I/O

I/O

I/O

I/O

VCCO

GND

I/O

I/O

I/O

I/O

-

I

O

I

-

I

I

I

I

-

I

-

I

O

I

I

-

-

-

I

I

-

-

DGND

for CPLD data writing (JTAG pin)

Digital audio signal output

(to +3.3V

D

)

Digital audio signal input

(to +3.3V

D

)

DGND

(to +3.3V

D

)

IDE READ signal (active-low)

IDE WRITE signal (active-low)

DMA ACKNOWLEDGE signal (active-low)

DMA REQUEST signal(active-low)

Power 3.3V

D

DMA CLEAR signal (active-low)

(to +3.3V

D

)

DGND

INTERRUPT signal (HDD to CPU) (active-high)

INTERRUPT signal (HDD to CPU) (active-low)

(to +3.3V

D

)

Bit clock for data between DGA and MAT

Clock for CPLD data communication (JTAG pin)

Power 3.3V

D

DGND

(to +3.3V

D

)

DGND

Power 3.3V

D

(to +3.3V

D

)

Master clock (22.5792KHz)

Bit clock for data between SWP50 and MAT (11.2894MHz)

(to +3.3V

D

)

Power 3.3V

D

DGND

(to +3.3V

D

)

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

GND

TMS

MELO_0

I/O

MELO_2

MELI_0

GND

I/O

I/O

I/O

I/O

I

VCCO

I/O

I/O

I/O

DGAMCLK

GND

DGAWCLK

I/O

IDEMARQ512D

DMAERR

I

TDD

VCCO

GND

I

I/O

WCLK1

I/O

WCLK0

GND

VCCO

ADLR

I/O

FS640UT

I/O/GOE1

FS

FS256

VCCO

I/O/GOE0

I/O

I/O

I/O

VCCO

GND

I/O

I/O

I/O

IDMARQ_0512HDL

-

O

O

I

-

-

O

-

O

O

O

I

O

-

O

O

-

-

O

O

I

I

-

-

-

O

DGND

for CPLD data communication (JTAG pin)

Data for Playback tracks1 and 2

(to +3.3V

D

)

Data for PLAYBACK tracks 3 and 4

Data for RECORD tracks 1 and 2

DGND

(to +3.3V

D

)

Power 3.3V

D

(to +3.3V

D

)

System master clock (22.5792MHz)

DGND

System word clock (44.1kHz)

(to +3.3V

D

)

IDE DMA request

(Not used)

(to DGND)

for CPLD data communication

Power 3.3V

D

DGND

(to +3.3V

D

)

(to DGND)

Word clock for DAC (Not used)

(to DGND)

Word clock for DAC (Not used)

DGND

Power 3.3V

D

LR signal for DAC (Not used)

(to DGND)

Maste clock for DAC (Not used)

(to DGND)

Sampling frequency (44.1kHz)

256FS (11.2896MHz)

Powe 3.3V

D

(to +3.3V

D

)

Power 3.3V

D

Ground

(to +3.3V

D

)

Output in case that the DMA request

signal is negated by the rising or falling

edge of 512FS. (Not used.)

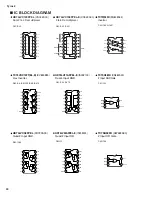

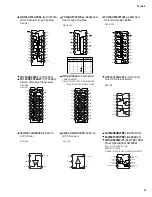

LC4256V-75TN100 CP

(X6046B00)

CPLD

(MEL)