40

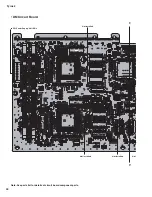

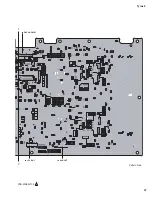

Tyros2

MO

TR

OWNE

BEDIE

MODE

■

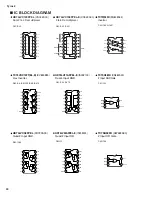

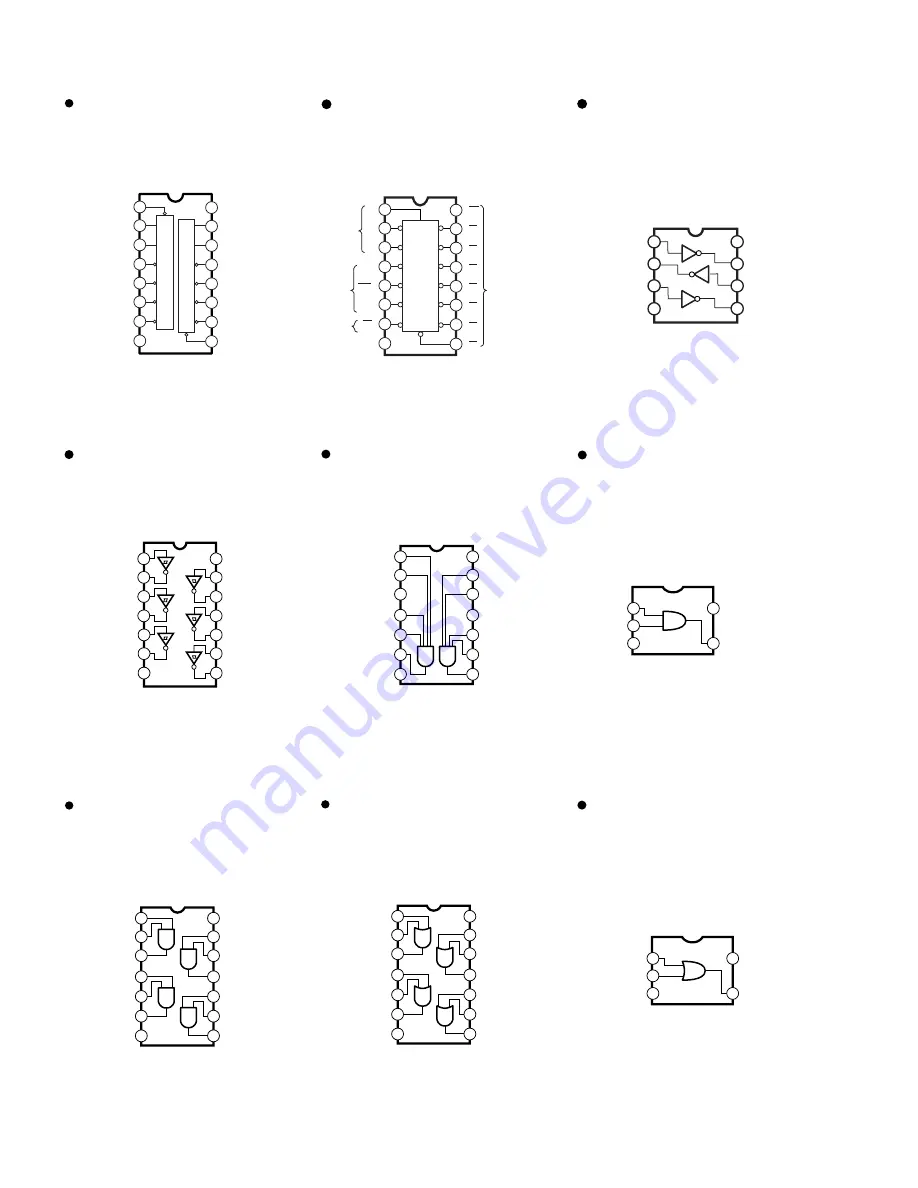

IC BLOCK DIAGRAM

1

2

3

4

5

6

7

1G

1A

1B

1Y0

1Y1

1Y2

1Y3

A

B

Y0

Y1

Y2

Y3

16

15

14

13

12

11

10

VCC

2G

2A

2B

2Y0

2Y1

2Y2

8

GND

9

2Y3

A

G

G

B

Y0

Y1

Y2

Y3

HD74LVC139FPEL

(XS048A00)

Dual 2 to 4 Demultiplexer

1

2

3

4

5

6

7

A

B

Select

Enable

Output

B

C

C

G2A

G2A

G2B

G2B

G1

G1

Y7

Y7

16

15

14

13

12

11

10

Vcc

Y0

Y0

Y1

Y1

Y2

Y2

Y3

Output

Y3

Y4

Y4

Y5

Y5

8

GND

9

Y6

A

Y6

HD74LVC138FPEL-E

(XS963A00)

3 to 8 Demultiplexer

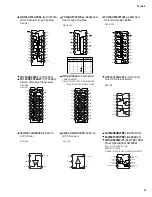

Vss

3A

2Y

VDD

1

2

3

4

5

6

7

8

1A

3Y

2Y

1Y

TC7W04FU

(XQ805A00)

Inverter

Hex Inverter

1

1A

2

1Y

3

2A

4

2Y

5

3A

6

3Y

7

GND

1

VDD

2

6A

3

6Y

4

5A

5

5Y

6

4A

7

4Y

TC74VHC14FT(EL,K)

(XV890B00)

HD74LV21AFPEL-E

(IS002100)

Dual 4 Input AND

1

2

3

1A

NC

4

1C

5

1D

6

1Y

7

GND

1B

14

13

12

Vcc

2C

11

NC

10

2B

9

2A

8

2Y

2D

TC7SH08FU

(XR680A00)

2 Input AND Gate

1

5

2

3

4

IN B

GND

Vcc

OUT Y

IN A

HD74LVC08FPEL

(XU720A00)

Quad 2 Input AND

1

2

3

1A

1Y

4

2A

5

2B

6

2Y

7

VSS

1B

14

13

12

VDD

4A

11

4Y

10

3B

9

3A

8

3Y

4B

TC7SH32FU

(XW633A00)

2 Input OR Gate

1

5

2

3

4

IN B

GND

Vcc

OUT Y

IN A

HD74LV32AFPEL-E

(IS003200)

Quad 2 Input OR

1

2

3

1A

1Y

4

2A

5

2B

6

2Y

7

GND

1B

14

13

12

Vcc

4A

11

4Y

10

3B

9

3A

8

3Y

4B