AD8HR

13

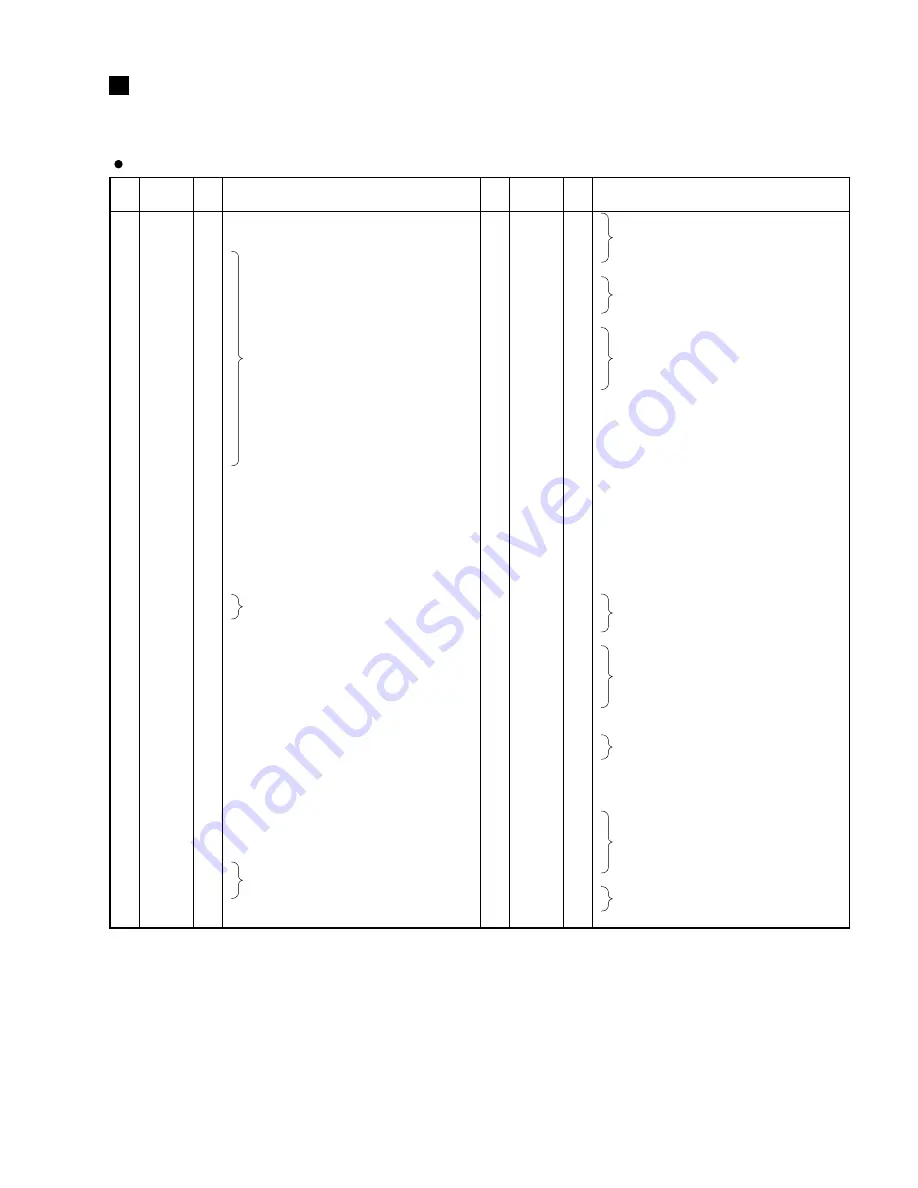

LSI PIN DESCRIPTION

(LSI 端子機能表)

PIN

NO.

I/O

FUNCTION

NAME

PIN

NO.

I/O

FUNCTION

NAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

TIOC4/DACK0/PE14

PE15

VSS

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

VCC

A17

VSS

/RAS/PB2

/CASL/PB3

/CASH/PB4

VSS

/RDWR / PB5

A18//BACK/PB6

A19//BREQ/PB7

A20/PB8

A21/PB9

VSS

/RD

/WDTOVF

/WRH

VCC

/WRL

VSS

/CS1

/CS0

/IRQ3/TCLKD/PA9

TCLKC//IRQ2 /PA8

/CS3

/CS2

/IRQ1/PA5

TXD1

RXD1

/IRQ0/PA2

TXD0

RXD0

D15

D14

D13

VSS

D12

I/O

O

I

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I

O

I

I/O

I/O

I/O

I

I/O

I/O

I/O

O

O

I

O

O

O

I

O

I

O

O

I/O

I/O

O

O

I/O

O

I

I/O

O

I

I/O

I/O

I/O

I

I/O

MTU I/O / DMA acknowledge / Port E

Port E

Ground

Address bus

Power supply

Address bus

Ground

Row address strobe / Port B

Column address strobe (low) / Port B

Column address strobe (high) / Port B

Ground

DRAM read / write / Port B

Address bus / Bus acknowledge / Port B

Address bus / Bus request / Port B

Address bus/ Port B

Ground

Read

Watch dog timer overflow

High write

Power supply

Low write

Ground

Chip select

Chip select

Interrupt request / Timer clock/ Port A

Timer clock / Interrupt request / Port A

Chip select

Chip select

Interrupt request / Port A

Data transmission

Data reception

Interrupt request / Port A

Data transmission

Data reception

Data bus

Ground

Data bus

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

D11

D10

D9

D8

VSS

D7

D6

D5

VCC

D4

D3

D2

D1

D0

VSS

XTAL

MD3

EXTAL

MD2

NMI

VCC

MD1

MD0

PLLVCC

PLLCAP

PLLVSS

PA15 / CK

/RES

PE0/DREQ0

PE1/DRAK0

PE2

PE3

PE4

VSS

PF0 / AN0

PF1 / AN1

PF2 / AN2

PF3 / AN3

PF4 / AN4

PF5 / AN5

AVSS

PF6 / AN6

PF7 / AN7

AVCC

VSS

PE5

VCC

PE6

PE7

PE8

PE9

PE10

VSS

PE11

PE12

/MRES

I/O

I/O

I/O

I/O

I

I/O

I/O

I/O

I

I/O

I/O

I/O

I/O

I/O

I

I

I

I

I

I

I

I

I

I

I

I

O

I

I/O

O

O

O

O

I

I

I

I

I

I

I

I

I

I

I

I

O

I

I/O

I/O

I/O

O

O

I

O

O

I

Data bus

Ground

Data bus

Power supply

Data bus

Ground

Crystal oscillator

Mode control

Crystal oscillator

Mode control

Non-maskable interrupt request

Power supply

Mode control

Mode control

PLL Power supply

PLL capacitor

PLL Ground

Port A / Clock

Power on reset

Port E / DMA request

Port E / DMA acknowledge

Port E

Ground

Port F / Analog input

Analog ground

Port F / Analog input

Power supply

Ground

Port E

Power supply

Port E

Ground

Port E

Manual reset

HD6437042AF53 (XY721A00) CPU

MAIN: IC2