AD8HR

19

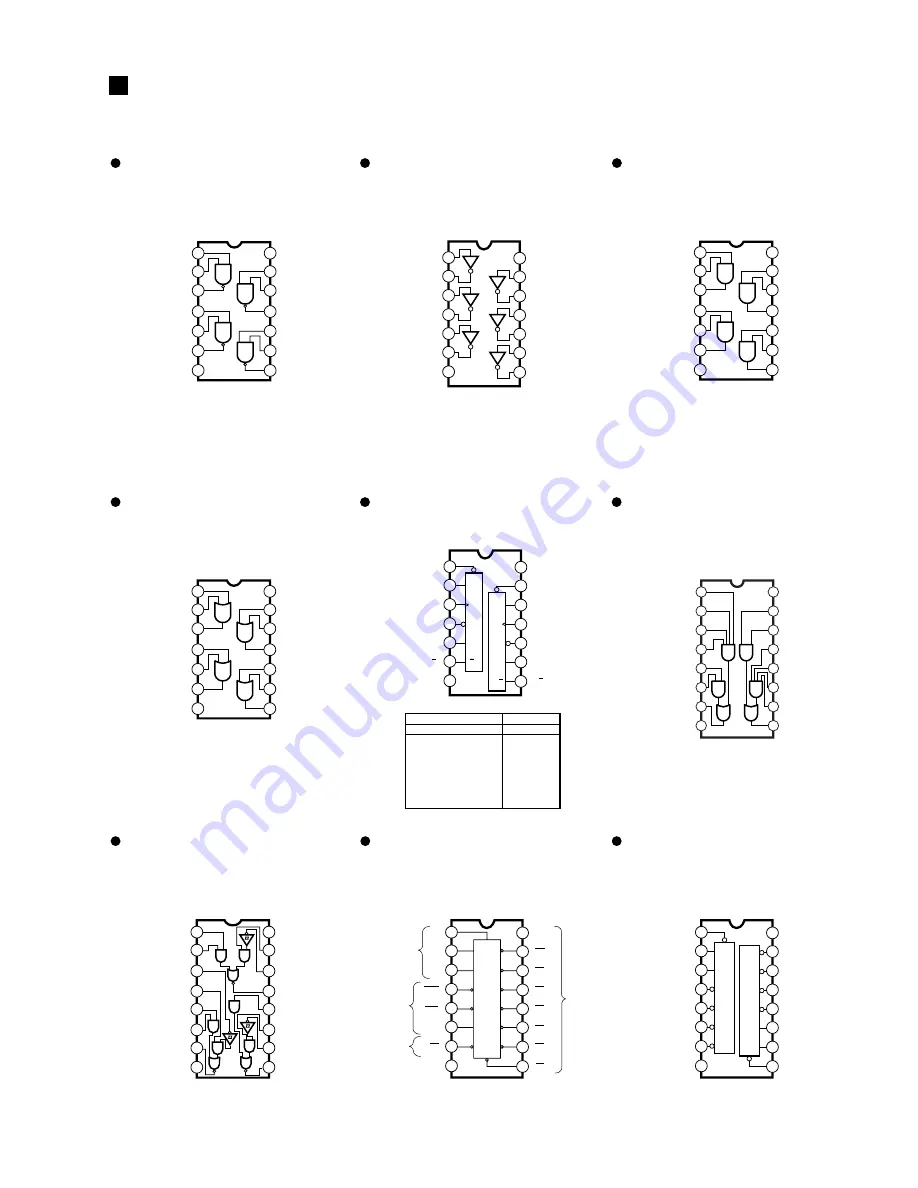

IC BLOCK DIAGRAM

TC74VHC00FT

(X2313A00)

Quad 2 Input NAND

MAIN: IC53

HD74LVU04AFPEL

(XY102A00)

Hex Inverter

MAIN: IC7

TC74VHC08FT

(XV891A00)

Quad 2 Input AND

MAIN: IC61,901

HD74LV32AFPEL

(IS003200)

Quad 2 Input OR

MAIN: IC12

SN75124NSR

(XV930A00)

Triple Line Receiver

MAIN: IC925

SN74LV138ANSR

(IS013810)

3 to 8 Demultiplexer

MAIN: IC962

SN74LV139ANSR

(IS013910)

Dual 2 to 4 Demultiplexer

MAIN: IC16

1

2

3

1A

1Y

4

2A

5

2B

6

2Y

7

Vss

1B

14

13

12

VDD

4A

11

4Y

10

3B

9

3A

8

3Y

4B

1

2

3

4

5

6

7

1A

1Y

2A

2Y

3A

3Y

Vss

14

13

12

11

10

9

8

VDD

6A

6Y

5A

5Y

4A

4Y

1

2

3

1A

1Y

4

2A

5

2B

6

2Y

7

VSS

1B

14

13

12

VDD

4A

11

4Y

10

3B

9

3A

8

3Y

4B

1

2

3

1A

1Y

4

2A

5

2B

6

2Y

7

GND

1B

14

13

12

Vcc

4A

11

4Y

10

3B

9

3A

8

3Y

4B

HD74LV74AFPEL

(IS007400)

Dual D-Type Flip-Flop

MAIN: IC6

SN75121NSR

(XU816A00)

Dual Line Driver

MAIN: IC926

INPUTS

OUTPUTS

PR

CLR

CLK

D

Q

Q

L

H

H

L

H

Q

O

H

L

H

H

L

Q

O

X

X

X

H

L

X

X

X

X

f

f

L

H

L

L

H

H

H

L

H

L

H

H

H

1

2

3

4

5

6

7

1CLR

1D

1CK

1PR

1Q

1Q

GND

14

13

12

11

10

9

8

VCC

2CLR

CLR

2D

D

2CK

CK

2PR

PR

2Q

2Q

Q

Q

CLR

D

CK

PR

Q

Q

Vcc

2F

2E

2A

2Y

GND

1Y

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

2C

2B

2D

1A

1B

1C

1D

1E

1F

1A

1B

2R

2S

2A

2B

2Y

GND

1

16

2

15

3

14

4

13

5

12

6

11

7

10

8

9

Vcc

1S

1R

1Y

3A

3S

3R

3Y

1

2

3

4

5

6

7

A

A

Select

Enable

Output

Output

B

B

C

C

G2A

G2A

G2B

G2B

G1

G1

Y7

Y7

Y5

Y4

Y3

Y2

Y1

Y0

Y6

16

15

14

13

12

11

10

Vcc

YO

Y1

Y2

Y3

Y4

Y5

8

GND

9

Y6

1

2

3

4

5

6

7

1G

1A

1B

1Y0

1Y1

1Y2

1Y3

A

G

B

Y0

Y1

Y2

Y3

16

15

14

13

12

11

10

Vcc

2G

2A

2B

2Y0

2Y1

2Y2

8

GND

9

2Y3

Y2

Y3

Y1

Y0

B

A

G

(IC ブロック図)