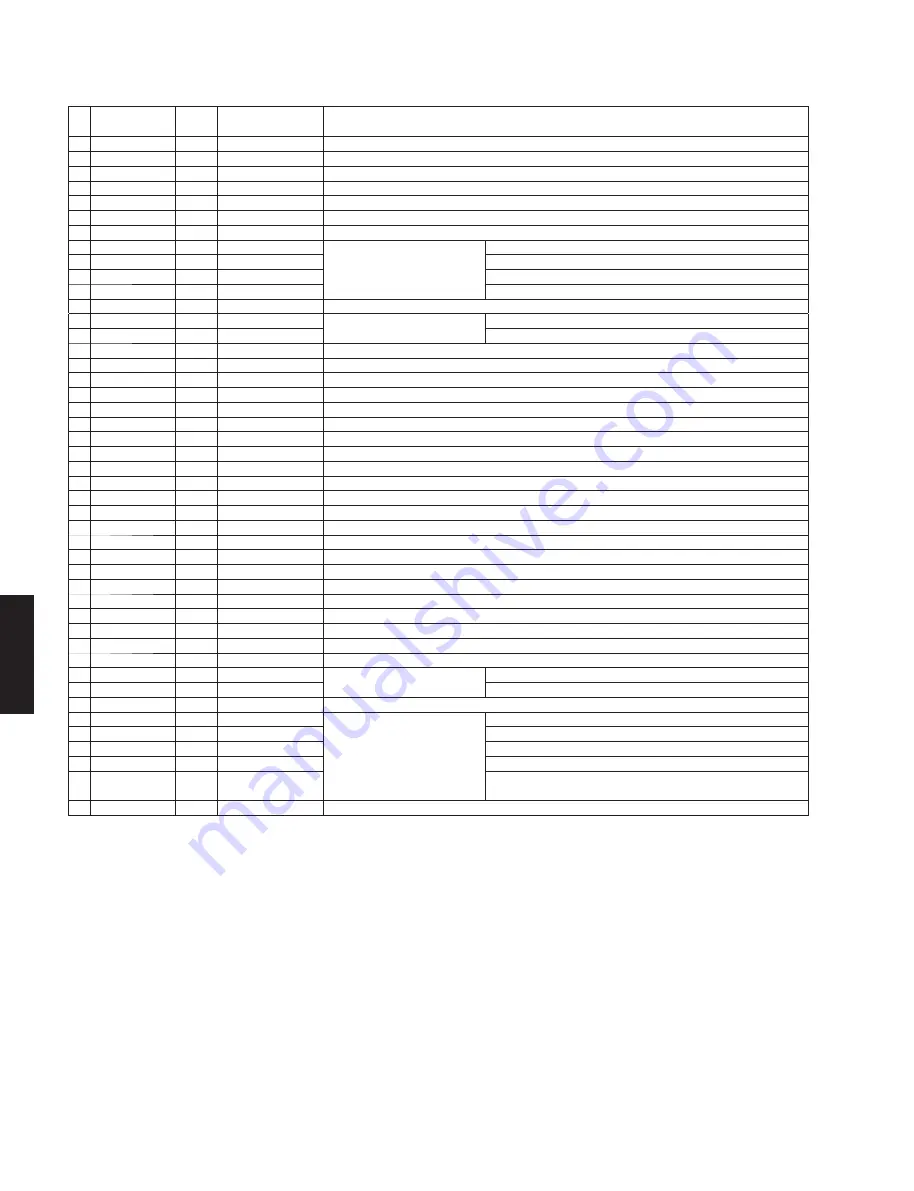

24

CD-S300

CD-S30

0

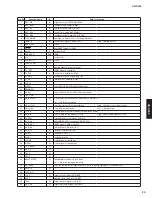

Pin

No.

Function

Name

I/O

State During a Reset

Detail of Function

36 DVDD

—

—

Digital system power supply

37 DVSS

—

—

Digital system ground / This pin must be connected to the 0 V level

38 DVDD15

AO

High

Digital circuit power supply capacitor connection

39 VVDD3

—

—

Internal PLL power supply

40 VVSS3

—

—

Internal PLL ground / This pin must be connected to the 0 V level

41 DVDD

—

—

Digital system power supply

42 DVSS

—

—

Digital system ground / This pin must be connected to the 0 V level

43 CE

I

Input

Host microprocessor interface

Host I/F : Chip enable signal input

44 CL

I

Input

Host I/F : Data transfer clock input

45 DI

I

Input

Host I/F : Data input

46 DO

O

Hi-Z (H)

Host I/F : Data output (Trial-state output)

47 RESB

I

—

IC reset input / This pin must be set low once after power is first applied

48 REG_READY0

O

Low

Host microprocessor interface

Host I/F : REG_READY output (Nch-opendrain output)

49 SUB_READY0

O

Low

Host I/F : SUB_READY output (Nch-opendrain output)

50 CONT2

I/O

Input

General purpose input/output

51 CONT1

I/O

Input

General purpose input/output

52 CONT0

I/O

Input

General purpose input/output

53 MODE

I

—

Set input / This pin must be connected to the DVDD

54 STREQ

I/O

Input

Stream data demand signal output

55 STCK

I/O

Input

Stream data bit clock input

56 STDATA

I/O

Input

Stream data input

57 TEST

I

—

Test input / This pin must be connected to the 0 V level

58 DATA

I/O

Input

Monitor pin / Audio data output

59 DATACK

I/O

Input

Monitor pin / Audio bit clock output

60 LRSY

I/O

Input

Monitor pin / Audio Left/Right channel clock output

61 DVDD

—

—

Digital system power supply

62 PCMLRSY

O

Low

Monitor pin / Audio Left/Right channel clock output

63 PCMBCK

O

Low

Monitor pin / Audio data shift clock output

64 PCMDATA

O

Low

Monitor pin / Audio data serial output

65 PCMREQ

I

Input

Monitor pin / Audio data output request signal input

66 DVDD15

AO

High

Digital circuit power supply capacitor connection

67 DVSS

—

—

Digital system ground / This pin must be connected to the 0 V level

68 DVDD

—

—

Digital system power supply

69 DOUT

O

Low

Monitor pin / Digital audio data output (EIAJ format)

70 CONT4

I/O

Input (Low)

General purpose input/output 4 (Initial : Input, internal pull-down resistor ON)

71 XVSS

—

—

Oscillator ground / This pin must be connected to the 0 V level

72 XOUT

O

Oscillation

Oscillation

16.9344 MHz oscillation pins

73 XIN

I

Oscillation

16.9344 MHz oscillation pins

74 XVDD

—

—

Oscillator power supply

75 LRVDD

—

—

D/A Converter

Left/Right channel power supply

76 LCHO

AO

LRVDD/2

Left channel output

77 LRREF

AO

LRVDD/2

Reference output for Left/Right channel

78 RCHO

AO

LRVDD/2

Right channel output

79 LRVSS

—

—

Left/Right channel ground

This pin must be connected to the 0 V level

80 SLCO

AO

Undefined

Slice level control output

Note

①

For the unused pins:

• The unused input pins must be connected to the GND (0 V) level

• The unused output pins must be leave open (No connection)

• The unused input/output pins must be connected to the GND (0 V) or power supply pin for I/O in input pin mode or must be left open (No connection) in

output pin mode

②

NC pins must be left open

③

For power supply pins:

• Same voltage must be supplied to DVDD, AVDD, XVDD, LRVDD, VVDD1, VVDD3 power supply pins (Refer to allowable operating ranges)

④

MODE pin must be connected to the DVDD

⑤

TEST pins must be connected to GND (0 V)

⑥

During power-on, RESB pin must be set to “Low” for more than 20 ms

⑦

Nch-opendrain output pin must put the pull-up resistance outside