A

1

2

3

4

5

6

7

8

9

10

B

C

D

E

F

G

H

I

J

K

L

M

N

CD-S3000

62

DIGITAL 2/3

★

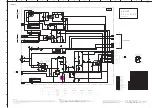

All voltages are measured with a 10MΩ/V DC electronic voltmeter.

★

Components having special characteristics are marked

⚠

and must be replaced

with parts having specifications equal to those originally installed.

★

Schematic diagram is subject to change without notice.

● 電圧は、内部抵抗 10MΩの電圧計で測定したものです。

● ⚠印のある部品は、安全性確保部品を示しています。部品の交換が必要な場合、

パーツリストに記載されている部品を使用してください。

● 本回路図は標準回路図です。改良のため予告なく変更することがあります。

DIGITAL IN

CD IN

1.5

3.3

3.3

5.0

R E M A R K S

C A P A C I T O R

P A R T S

N A M E

N O

N O

M A R K

M A R K

E L E C T R O L Y T I C

C A P A C I T O R

C E R A M I C

C A P A C I T O R

P O L Y E S T E R F I L M

C A P A C I T O R

P O L Y S T Y R E N E

F I L M

C A P A C I T O R

M I C A

C A P A C I T O R

P O L Y P R O P Y L E N E

F I L M

C A P A C I T O R

S E M I C O N D U C T I V E

C E R A M I C C A P A C I T O R

P

T A N T A L U M

C A P A C I T O R

T U B U L A R

C A P A C I T O R

C E R A M I C

R E S I S T O R

R E M A R K S

N O M A R K

P A R T S

N A M E

C A R B O N

C A R B O N

M E T A L

M E T A L

M E T A L

F I R E

C E M E N T

S E M I

F I L M

R E S I S T O R

F I L M

R E S I S T O R

O X I D E

F I L M

R E S I S T O R

F I L M

R E S I S T O R

P L A T E

R E S I S T O R

P R O O F C A R B O N

F I L M

R E S I S T O R

M O L D E D

R E S I S T O R

V A R I A B L E

R E S I S T O R

( P = 5 )

( P = 1 0 )

C H I P

R E S I S T O R

N O T I C E

U . S . A

G

C A N A D A

E U R O P E

L

C H I N A

A U S T R A L I A

S I N G A P O R E

K O R E A

G E N E R A L

U

C

T

A

K

R

J A P A N

( m o d e l )

B

B R I T I S H

J

S O U T H E U R O P E

E

V

T A I W A N

F

R U S S I A N

P

L A T I N A M E R I C A

S

B R A Z I L

H

T H A I

L : P C M H : D S D

D I R / D I T

P C M / D S D

S e l e c t

A V - 3

GNDD

R_DATA

DSDPCM

GNDD

GNDD

XCSO2

LRCK

GNDD

GNDD

SO

BCLK/DSDCLK

SCL

MCLK

DATA/L_DATA

XCSO1

GNDD

GNDD

D _ L O C K

D A C _ S C L

D G N D

S E L _ S D O _ D S D R

S E L _ S P D I F _ D S D R

D G N D

S E L _ W C K _ D S D L

+ 1 2 R Y

- 1 2 R Y

D A C _ S D A

P R V _ L

M U T E

D G N D

R Y _ A U D I O

D G N D

D 3 . 3 V

D 3 . 3 V

S E L _ S D O _ D S D L

S E L _ B C K _ D S D C L K

D G N D

P R V _ R

D A C _ N _ R S T

D G N D

L:Other H:CD

T o C B 7 3 1

D G N D f o r D A C

T o Z o r a n M o d u l e

C E

V O U T

V D D

N C

G N D

G N D

D I R B Y P A S S

S e l e c t

L : D I R H : D I R B Y P A S S

T D O

T D I

T C K

T M S

( N C ) T R S T N

V C C

G N D

F P G A

T o S h t . 0 0 1

S A - C D M o d u l e

D I G I T A L

4 0 1

9 0 0

0 0 2 . s h t

S S P 2 P O N

COAX IN

OPT IN

COAX OUT

OPT OUT

to AUDIO(1)

001.sht CB1

(DAC)

to IC404

001.sht

(SYSTEM CPU)

(SSP2)

to IC401

003.sht

S Y S T E M C P U

T o I C 4 0 4

T o I C 4 0 4

S Y S T E M C P U

S Y S T E M C P U

T o I C 4 0 4

T o I C 4 0 1

S S P 2

D e s t i n a t i o n P a r t L i s t

+ - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - +

| s X X | L O C | J | U T K A L V | B | G |

+ - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - +

| s 4 0 1 | C 4 5 0 | U R 2 3 8 1 0 | U R 2 3 8 1 0 | U U 2 3 8 1 0 | U U 2 3 8 1 0 |

| | | 1 0 0 / 1 6 | 1 0 0 / 1 6 | 1 0 0 / 1 6 | 1 0 0 / 1 6 |

+ - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - +

| s 4 0 2 | C 4 6 0 | U U 2 6 7 1 0 | U U 2 6 7 1 0 | U U 2 3 7 1 0 | U U 2 3 7 1 0 |

| | | 1 0 / 5 0 | 1 0 / 5 0 | 1 0 / 1 6 | 1 0 / 1 6 |

+ - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - +

| s 4 0 3 | C 5 8 1 | U R 2 3 8 1 0 | U R 2 3 8 1 0 | U U 2 3 8 1 0 | U U 2 3 8 1 0 |

| | | 1 0 0 / 1 6 | 1 0 0 / 1 6 | 1 0 0 / 1 6 | 1 0 0 / 1 6 |

+ - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - + - - - - - - - - - - - - - - - +

D I R _ N _ C S

D I R _ N _ R S T

D I R _ N _ I N T

D I R _ M I S O

D I R _ M O S I

D I R _ S C K

DOUT

DIR_BCK

DIR_WCK

DIR_SDO

C O A X I N

C O A X I N

D O U T

I2SSEL_DSDPCM

PI_DSDR

D I N

R Y _ A U D I O 2

D A C _ S C L

D A C _ S D A

D A C _ N _ R S T

D I R _ N _ I N T

D I R _ M I S O

D I R _ M O S I

D I R _ S C K

D I R _ N _ C S

D I R _ N _ R S T

P R V R

P R V L

D A C _ S D A

D A C _ S C L

D A C _ N _ R S T

PI_BCK_DSDCLK

PI_SDO_DSDL

P I _ S P D I F

S W _ C D _ O T H E R

P R V L

P R V R

R Y _ A U D I O 2

I 2 S S E L _ D S D P C M

S E L _ D I R _ B Y P A S S

D O U T

S E L _ S D O _ D S D L

S E L _ S D O _ D S D R

S E L _ W C K _ D S D L

S E L _ S P D I F _ D S D R

S E L _ B C K _ D S D C L K

SEL_DIR_BYPASS

D I R _ B C K

P I _ B C K _ D S D C L K

D I R _ W C K

P I _ W C K

D I R _ S D O

P I _ D S D R

PI_WCK

D I N

S S P 2 _ S P D I F

S S P 2 _ W C K

S S P 2 _ M C K

S S P 2 _ S D O 0

S S P 2 _ S P D I F

S S P 2 _ S D O 0

S S P 2 _ W C K

S S P 2 _ B C K

S S P 2 _ M C K

S S P 2 _ B C K

P I _ S P D I F

F P G A _ S P D I F _ D S D R

F P G A _ W C K _ D S D L

F P G A _ S D O _ D S D L

F P G A _ S D O _ D S D R

F P G A _ B C K _ D S D C L K

SW_CD_OTHER

PI_MCK

DIR_MCK

S E L _ S D O _ D S D R

S E L _ S D O _ D S D L

S E L _ W C K _ D S D L

S E L _ B C K _ D S D C L K

S E L _ S P D I F _ D S D R

F P G A _ I N I T N

F P G A _ D O N E

F P G A _ R R E S E T

F P G A _ S E L C

F P G A _ S E L B

F P G A _ S E L A

F P G A _ D S D M U T E

F P G A _ D O P _ D S D R A T E

F P G A _ D O P _ D S D P C M

F P G A _ P R O G

F P G A _ I O 2

F P G A _ I O 1

F P G A _ I O 0

S S P 2 _ S D O 1

F P G A _ J T A G E N

S S P 2 _ S D O 0

S S P 2 _ M C K

S S P 2 _ B C K

S S P 2 _ W C K

S S P 2 _ S D O 1

S S P 2 _ S P D I F

F P G A _ I O 0

F P G A _ I O 1

F P G A _ I O 2

F P G A _ D O P _ D S D P C M

F P G A _ D O P _ D S D R A T E

F P G A _ D S D M U T E

F P G A _ S E L A

F P G A _ S E L B

F P G A _ S E L C

F P G A _ R R E S E T

D I R _ B C K

D I R _ W C K

D I R _ S D O

D O U T

P I _ W C K

P I _ D S D R

P I _ S D O _ D S D L

P I _ B C K _ D S D C L K

P I _ M C K

F P G A _ S P D I F _ D S D R

F P G A _ B C K _ D S D C L K

F P G A _ W C K _ D S D L

F P G A _ S D O _ D S D L

F P G A _ S D O _ D S D R

F P G A _ D O N E

F P G A _ I N I T N

F P G A _ P R O G

F P G A _ J T A G E N

S E L _ D I R _ B Y P A S S

I 2 S S E L _ D S D P C M

D I R _ M C K

P I _ S D O _ D S D L

D A C _ A _ M U T E

D A C _ A _ M U T E

C 5 4 5

1 0 / 6 . 3

D G N D

C539

10/6.3

+ 3 . 3 D I R

DGND

DGND

DGND

E R R O R / I N T 0

N P C M / I N T 1

M P I O _ A 0

M P I O _ A 1

M P I O _ A 2

M P I O _ A 3

M P I O _ C 0

M P I O _ C 1

M P I O _ C 2

0 M P I O _ C 3

M P I O _ B 0

M P I O _ B 1

MPIO_B2

MPIO_B

3

MPO0

MPO1

DOUT

LRCK

BCK

SCKO

DGND

DVDD

MDO/ADR0

MDI/SD

A

M C / S C L

M S / A D R 1

M O D E

R X I N 7 / A D I N 0

R X I N 6 / A L R C K I 0

R X I N 5 / A B C K I 0

R X I N 4 / A S C K I 0

R X I N 3

R X I N 2

R S T

R X I N 1

V D D R X

RXIN

0

GNDRX

XTI

XTO

AGN

D

VCC

FILT

VCOM

AGNDAD

VCCAD

VINL

VIN

R

+ 3 . 3 D I R

+ 3 . 3 D I R

D G N D

C551

0.068/25

D G N D

+ 3 . 3 D I R

C524

10/6.3

D A C _ S D A

D A C _ S C L

R Y _ A U D I O 2

R 6 1 1

1 0 0

R 6 1 3

1 0 0

R 6 6 3

1 0 K

R 6 6 4

1 0 K

R 6 6 5

1 0 K

R 6 5 4

1 0 0

R 6 6 6

1 0 0

R 6 5 5

1 0 0

R 6 6 7

1 0 0

R657

100

R651

100

R648

100

R645

100

R 6 1 8 1 0 K

R 6 1 9

1 0 K

R 6 2 9

1 0 K

+3.3DIR

R 7 1 8

n o _ u s e

C 5 8 7

n o _ u s e

R 7 0 9

n o _ u s e

R 7 1 1 n o _ u s e

L421

no_use

C586

no_use

R 7 0 8

n o _ u s e

D G N D

D I R _ N _ R S T

D I R _ M I S O

D I R _ M O S I

D I R _ N _ I N T

R 6 0 4

6 8 0

C516

0.1/16

R 6 0 5

4 . 7 K

C506

no_use

C 5 0 9

0 . 1 / 1 6

R 6 0 7

1 8 K

L 4 0 6

B L M 2 1 P G 6 0 0 S N 1 D

C503

0.01(B)

R 6 0 6

3 3

C 5 1 3

3 3 / 1 6

C 5 0 5

0 . 0 1 ( B )

R 6 0 8

3 3

R 6 0 3

3 3

C508

no_use

+5D

D G N D

D433

no_use

D432

no_use

D I R _ S C K

D I R _ N _ C S

R653

10

R669

10

R656

10

R649

no_use

R650

no_use

R661

no_use

R647

no_use

R 6 2 3

1 0

L 4 1 4

B K 1 6 0 8 L M 2 5 2 - T

L 4 1 8

B K 1 6 0 8 L M 2 5 2 - T

L 4 1 5

B K 1 6 0 8 L M 2 5 2 - T

C537

0.1/16

C546

0.1/16

C542

0.1/16

C522

470P(SL)

C555

4700P(B)

C 5 5 6

4 7 0 0 P ( B )

R 6 1 5

1 0 0

R 6 1 6 1 0 0

1 0 0 K

R 6 1 2

R 6 3 1

n o _ u s e

R639

680

R 6 5 9

3 3

R673

10K

R 6 2 8

1 0 K

R 6 6 2

1 0 K

R636

33

R 6 3 0

3 3

R 6 5 2

3 3

R640

33

R638

33

C521

100/1

6

IC428

no_use

1

S E L E C T

2

1 A

3

1 B

4

1 Y

5

2 A

6

2 B

7

2 Y

8

G N D

9

3 Y

10

3 B

11

3 A

12

4 Y

13

4 B

14

4 A

15

S T

16

V C C

D A C _ N _ R S T

DGND

R 7 0 5 n o _ u s e

R690

no_use

R 7 0 6

n o _ u s e

R 7 0 4 n o _ u s e

+ 3 . 3 D I R

C 5 8 4 n o _ u s e

R 7 2 4

n o _ u s e

R 7 2 3

n o _ u s e

R 7 0 1

n o _ u s e

IC427

no_use

1

S E L E C T

2

1 A

3

1 B

4

1 Y

5

2 A

6

2 B

7

2 Y

8

G N D

9

3 Y

10

3 B

11

3 A

12

4 Y

13

4 B

14

4 A

15

S T

16

V C C

R 7 2 5

n o _ u s e

R 7 1 7 n o _ u s e

D G N D

C 5 8 5 n o _ u s e

R 7 0 3 n o _ u s e

L420

no_use

R726

no_use

R 7 0 2 n o _ u s e

R 7 1 9

n o _ u s e

R 7 2 0

n o _ u s e

R 7 2 1

n o _ u s e

R 7 2 2

n o _ u s e

P R V L

P R V R

+ 3 . 3 D A C

D G N D

- 1 2 R Y

+ 1 2 R Y

R 7 2 8

1 0 0

R 7 3 4

1 0 0

R 7 2 9

1 0 0

C594

no_use

C596

no_use

C B 4 0 7

1 7 F M N - B T K - A ( L F )

M O _ G N D

J424

no_use

J423

no_use

J422

no_use

D G N D

J418

no_use

C599

no_use

R 7 3 5

n o _ u s e

R 7 3 3

n o _ u s e

R 7 3 2

n o _ u s e

R 7 3 1

n o _ u s e

R 7 3 0

n o _ u s e

ST402

C592

no_use

C593

no_use

S W _ C D _ O T H E R

Q 4 0 8

n o _ u s e

Q407

no_use

R683

no_use

R687

no_use

R680

no_use

G 4 0 2

S D 0 0 4 3 3 - 2 1

G

R685

no_use

R 5 9 9

2 . 2

F G 2

C595 no_use

C597

no_use

C598

no_use

C 5 4 7

n o _ u s e

C 5 5 3

n o _ u s e

C 5 4 8

n o _ u s e

C 5 5 4

n o _ u s e

C 5 4 9

n o _ u s e

J 4 0 4

n o _ u s e

J 4 0 5

n o _ u s e

J 4 0 6

n o _ u s e

J 4 0 7

n o _ u s e

Q 4 1 1

D T C 0 1 4 E U B T L

+ 3 . 3 D A C

C583

0.01(B)

L 4 2 2

B L M 1 8 P G 4 7 1 S N 1 D

C582

1000P(B)

C581

100/16

s403

Q 4 1 0

R A L 0 3 5 P 0 1

1

2

3

4

5

6

+ 3 . 3 U S B

+ 3 . 3 D I R

L 4 2 4

B L M 1 8 P G 4 7 1 S N 1 D

S S P 2 _ P O N

R 7 1 5

4 7 0

R710

680

L 4 2 3

B L M 1 8 P G 4 7 1 S N 1 D

R716

100K

I C 4 3 0

R 1 1 7 2 S 3 3 1 B - E 2 - F

C588

4.7/6.3

+ 5 D

C591

4.7/6.3

R 7 2 7

1 0 K

S S P 2 _ S D O 0

S S P 2 _ M C K

I 2 S S E L _ D S D P C M

C B 4 0 8

2 5 0 6 0 1 1 2 3 K 4

R 7 1 2

n o _ u s e

R 7 1 3

n o _ u s e

S E L _ D I R _ B Y P A S S

S S P 2 _ W C K

S S P 2 _ S P D I F

S S P 2 _ B C K

I C 4 3 7

n o _ u s e

1

SELECT

2

1A

3

1B

4

1Y

5

2A

6

2B

7

2Y

8

GND

9

3Y

1 0

3B

1 1

3A

1 2

4Y

1 3

4B

1 4

4A

1 5

ST

1 6

VCC

C635

no_use

J 4 4 2

n o _ u s e

J 4 4 3

n o _ u s e

J 4 4 4

n o _ u s e

R771

no_use

R772

no_use

R773

no_use

R774

no_use

R775

no_use

R776

no_use

R777

no_use

R778

no_use

R779

no_use

R780

no_use

R781

no_use

R782

no_use

D P W R _ O N

J 4 5 0

n o _ u s e

D G N D

D G N D

X L 4 0 3

2 4 . 5 7 6 M H Z

4

1

2

3

C544

10P(CH)

C538

10P(CH)

R633

56

V +

8

V -

4

I C 4 2 1

T C 7 W H U 0 4 F K

1

7

I C 4 2 1

T C 7 W H U 0 4 F K

3

5

I C 4 2 1

T C 7 W H U 0 4 F K

2

V +

8

V -

I C 4 2 0

T C 7 W H U 0 4 F K

7

I C 4 2 0

T C 7 W H U 0 4 F K

3

I C 4 2 0

2

L 4 0 7

P E 6 5 6 1 2 N L

1

2

3

4

C510

0.1/16

L 4 0 5

B L M 2 1 P G 6 0 0 S N 1 D

L 4 0 4

P E 6 5 6 1 2 N L

1

2

3

4

R 6 0 2

3 3

C504

10/16

C507

0.01(B)

C511

10/16

R601

75

C 5 8 0

3 3 / 1 6

R621

33

R 6 2 4

1 0 K

+ 1 . 5 U S B

L 4 2 5

B L M 1 8 P G 4 7 1 S N 1 D

L 4 2 7

B L M 1 8 P G 4 7 1 S N 1 D

C589

4.7/6.3

C590

4.7/6.3

L 4 2 9

B L M 1 8 P G 4 7 1 S N 1 D

+ 1 . 5 U S B 1

L 4 0 3

B L M 1 8 P G 4 7 1 S N 1 D

+ 3 . 3 U S B 1

P I _ S P D I F

0

J 4 5 1

0

J 4 5 2

0

J 4 5 3

0

J 4 5 4

0

J 4 5 5

L 4 3 0

B L M 1 8 P G 4 7 1 S N 1 D

+ 3 . 3 F P G A

C 6 8 7

1 / 2 5

C 6 8 8

1 / 2 5

C 6 8 9

1 / 2 5

C 6 9 0

1 / 2 5

C 6 9 1

1 / 2 5

+3.3FPGA

D G N D

C 7 0 1

0 . 1 / 1 6

R801

no_use

R 8 0 2

1 0 0

R 8 0 3

1 0 0

R 8 0 4

1 0 0

R 8 0 5

1 0 0

R 8 0 6

1 0 0

R 8 0 7

1 0 0

R 8 0 8

1 0 0

R 8 0 9

1 0 0

R 8 1 0

1 0 0

R 8 1 1

1 0 0

R 8 1 2

1 0 0

R 8 1 3

1 0 0

R 8 1 4

1 0 0

R 8 1 5

1 0 0

R 8 1 6

1 0 0

R 8 1 7

1 0 0

R 8 1 8

1 0 0

R 8 2 9

1 0 0

R 8 3 0

1 0 0

R 8 3 1

1 0 0

R 8 3 2

1 0 0

R834

no_use

F P G A _ D O P _ D S D P C M

F P G A _ I O 0

F P G A _ I O 1

F P G A _ S E L A

F P G A _ I O 2

F P G A _ S E L B

F P G A _ D S D M U T E

F P G A _ D O P _ D S D R A T E

F P G A _ D O N E

F P G A _ S E L C

F P G A _ R R E S E T

R 6 2 2

n o _ u s e

+ 3 . 3 F P G A

DGND

R 6 2 0

1 0 0

R 6 2 5

1 0 0

R 6 2 6

1 0 0

R 6 1 4

1 0 0

R597

10K

R598

10K

S S P 2 _ S D O 1

S S P 2 _ I O 0

S S P 2 _ I O 1

S S P 2 _ I O 2

S S P 2 _ I O 3

R 8 6 8

1 0 0

R 8 6 9

1 0 0

R 8 7 0

1 0 0

R 8 7 1

1 0 0

F P G A _ I N I T N

F P G A _ P R O G

F P G A _ J T A G E N

1

2

3

4

5

6

7

8

9

10

1 1

1 2

1 3

14

15

1 6

1 7

18

19

2 0

2 1

2 2

2 3

2 4

2 5

2 6

2 7

2 8

29

30

3 1

3 2

3 3

3 4

3 5

36

37

3 8

3 9

4 0

4 1

4 2

4 3

4 4

45

4 6

47

4 8

4 9

5 0

5 1

5 2

5 3

5 4

5 5

5 6

5 7

5 8

59

60

61

6 2

6 3

64

65

6 6

6 7

68

69

7 0

7 1

7 2

7 3

7 4

7 5

7 6

7 7

78

7 9

8 0

8 1

8 2

83

84

8 5

8 6

8 7

8 8

89

9 0

9 1

9 2

9 3

9 4

9 5

96

97

9 8

9 9

1 0 0

C 6 6 7

1 / 2 5

L601

BK1608LM252-T

C 6 6 8

1 / 2 5

C 6 6 9

1 / 2 5

C 6 8 6

1 / 2 5

C 7 0 0

1 / 2 5

C 7 0 4

1 / 2 5

C 7 0 5

1 0 / 6 . 3

R825

3.3K

R833

3.3K

R 8 1 9

1 0 0

R 8 2 0

1 0 0

R 8 2 1

1 0 0

R 8 2 2

1 0 0

R 8 2 3

1 0 0

R 8 2 4

1 0 0

R 8 2 6

1 0 0

R 8 2 7

1 0 0

R 8 2 8

1 0 0

R 8 7 4

1 0 0

R 8 7 5

1 0 0

R 8 7 6

1 0 0

R 8 3 5

1 0 0

R 8 7 7

1 0 0

R 8 7 8

n o _ u s e

R 8 7 9

n o _ u s e

R880

3.3K R881

3.3K

R 8 8 2

2 . 2 K

C B 4 1 3

0 7 F M N - B M T - A - T F T

A _ M U T E

S S P 2 _ Y I S O _ M U T E

D 4 3 7 1 S S 3 5 5 V M

D 4 3 8 n o _ u s e

R884

no_use

D G N D

J S R 2 1 6 5

U 4 0 1

VCC

1

G

2

OUT

3

M

A

E

T

L

O

S

2

0

4

U

G

VCC

IN

R 1 1 7 2 H 1 5 1 D - T 1 - F

I C 4 4 1

CEorCE

GND

NC

VDD

VOUT

0

J 4 5 9

0

J 4 6 0

P J 4 0 1

T 6 7 8 2 - A A A C

G

P J 4 0 2

T 6 7 8 2 - A A A C

G

D G N D

D G N D

R889

no_use

C709

0.01(B)

R 8 9 1

1 0 0

D A C _ A _ M U T E

R 6 0 9

3 3

R893

2.2

R894

2.2

C710

0.01(B)

C711

0.01(B)

D G N D

D G N D

R 8 9 5

6 8

C712

120P(SL)

C713

47P(CH)

R 6 0 0

6 8

C730

1000P(B)

0

J 4 6 2

0

J 4 6 3

C 5 7 2

1 0 0 0 P ( B )

C 5 7 1

1 0 0 0 P ( B )

L602

no_use

L603

no_use

R643

100

R 6 1 7

3 3

V

DD

CE

Pin No.

1

2

3

4

5

Symbol

V

OUT

GND

CE

NC

V

DD

Description

Output Pin of Voltage Regulator

Ground Pin

Chip Enable Pin

No Connection

Input Pin

Vref

5

4

2

1

Current Limit

V

OUT

GND

IC441

: R1172H151D-T1-FE

CMOS-based positive-voltage regulator IC

IC430

: R1172S331B-E2-F

CMOS-based positive-voltage regulator IC

V

DD

CE

Pin No.

1

2, 5

3

4

6

Symbol

V

OUT

GND

CE

NC

V

DD

Description

Output Pin of Voltage Regulator

Ground Pin

Chip Enable Pin

No Connection

Input Pin

Vref

6

1

3

2,5

Current Limit

V

OUT

GND

IC424

: PCM9210PTR

216-kHz digital audio interface transceiver (DIX) with stereo ADC and routing

PLL

DIT

MPO0/1

SELECTOR

MPIO_B

SELECTOR

MAIN

OUTPUT

PORT

ADC

Com. Supply

AUXIN1

ADC Standalone

ADC Mode

Control

MPIO_C

SELECTOR

OSC

SPI/I

2

C

INTERFACE

Reset and

Mode

Set

Divider

XMCKO

Divider

GPIO/GPO

Data

ADC

ANALOG

DIR

ANALOG

ALL

DIGITAL

Function

Control

DIT CS

(48-bit)

DIR CS

(48-bit)

DIR

Interrupt

DIR

Pc and Pd

All Port

Calculator

Is Calculator

DIR IS

Calculator

MPIO_A

MPIO_B

MPIO_C

MPO1

MPO0

REGISTER

POWER SUPPLY

XMCKO

(To MPIO_A and MPO0/1)

SBCK/SLRCK

(To MPIO_A)

Secondary SCK/LRCK

EXTRA DIR FUNCTIONS

Divider

Selector

ERROR DETECTION

Flags

Validity Flag

User Data

BFRAME Detection

Channel Status Data

Interrupt System

Non PCM DETECTION

DTS-CD/LD Detection

ADC Clock

(SCK/BCK/LRCK)

DIR

ADC

DITOUT

RECOUT1

AUXOUT

AUXIN2

RECOUT0

AUTO

DIR

ADC

DOUT

RXIN7

SCKO/BCK/LRCK

AUXIN0

AUXIN1

AUXIN2

Clock/Data

Recovery

Lock

Detection

Lock:DIR

Unlock:ADC

33

35

32

31

30

29

28

3

4

5

6

37

RXIN0

RXIN0

RXIN1

RXIN2

RXIN3

RXIN4

RXIN5

RXIN6

RXIN7

RXIN8

RXIN9

RXIN10

RXIN11

RECOUT0

RECOUT1

DITOUT

RXIN1

RXIN2

RXIN3

RXIN4/ASCKIO

RXIN5/ABCKIO

RXIN6/ALRCKIO

FILT

RXIN7/ADIN0

AUXIN0

MPIO_A0(CLKST)

MPIO_A1(VOUT)

MPIO_A2(XMCKO)

MPIO_A3(INT0)

SCKO

BCK

LRCK

DOUT

MPO0(TXOUT)

MPO1(VOUT)

MPIO_B0(ASCKI2)

MPIO_B1(ABCKI2)

MPIO_B2(ALRCKI2)

MPIO_B3(ADIN2)

48

47

44

VINL

VINR

VCOM

7

8

9

10

MPIO_C0(TXSCK)

MPIO_C1(TXBCK)

MPIO_C2(TXLRCK)

MPIO_C3(TXDIN)

39

40

25

24

34

27

46

23

26

XTI

XTO

MS/ADR1

MDO/ADR0

MC/SCL

MDI/SDA

RST

MODE

VCCAD AGNDAD SGND

VCC

VDD

AGND

DGND VDDRX

MPIO_A

SELECTOR

43

AUTO

DIR

ADC

AUXIN0

AUXIN1

AUXIN2

AUTO

DIR

ADC

AUXIN0

AUXIN1

AUXIN2

20

19

18

17

15

11

12

13

14

ERROR/INT0

NPCM/INT1

1

2

16

45

38

22

21

42

41

36

IC420, 421

: TC7WHU04FK

Triple inverter

8

1

1A

V

CC

7

2

3Y

1Y

6

3

2A

3A

5

4

GND

2Y

DIGITAL

OUT

No replacement part available.

サービス部品供給なし

to DIGITAL 3/3

to DIGITAL 1/3

to DIGITAL 1/3

to DIGITAL 1/3

to DIGITAL 1/3

to DIGITAL 1/3

to DIGITAL 3/3

to Module board_CN210

(For factory)

DIGITAL

IN

OPTICAL

COAXIAL

OPTICAL

COAXIAL

Summary of Contents for CD-S3000

Page 6: ... FRONT PANELS U K A B G L V J models T model 6 CD S3000 CD S3000 ...

Page 7: ... REAR PANELS U V models U model V model Bottom view 7 CD S3000 CD S3000 ...

Page 8: ...A B G L models K model T model A model B G models 8 CD S3000 CD S3000 ...

Page 9: ...J model 9 CD S3000 CD S3000 ...

Page 86: ...86 CD S3000 CD S3000 ...

Page 87: ...MEMO 87 CD S3000 CD S3000 87 ...

Page 88: ...CD S3000 ...