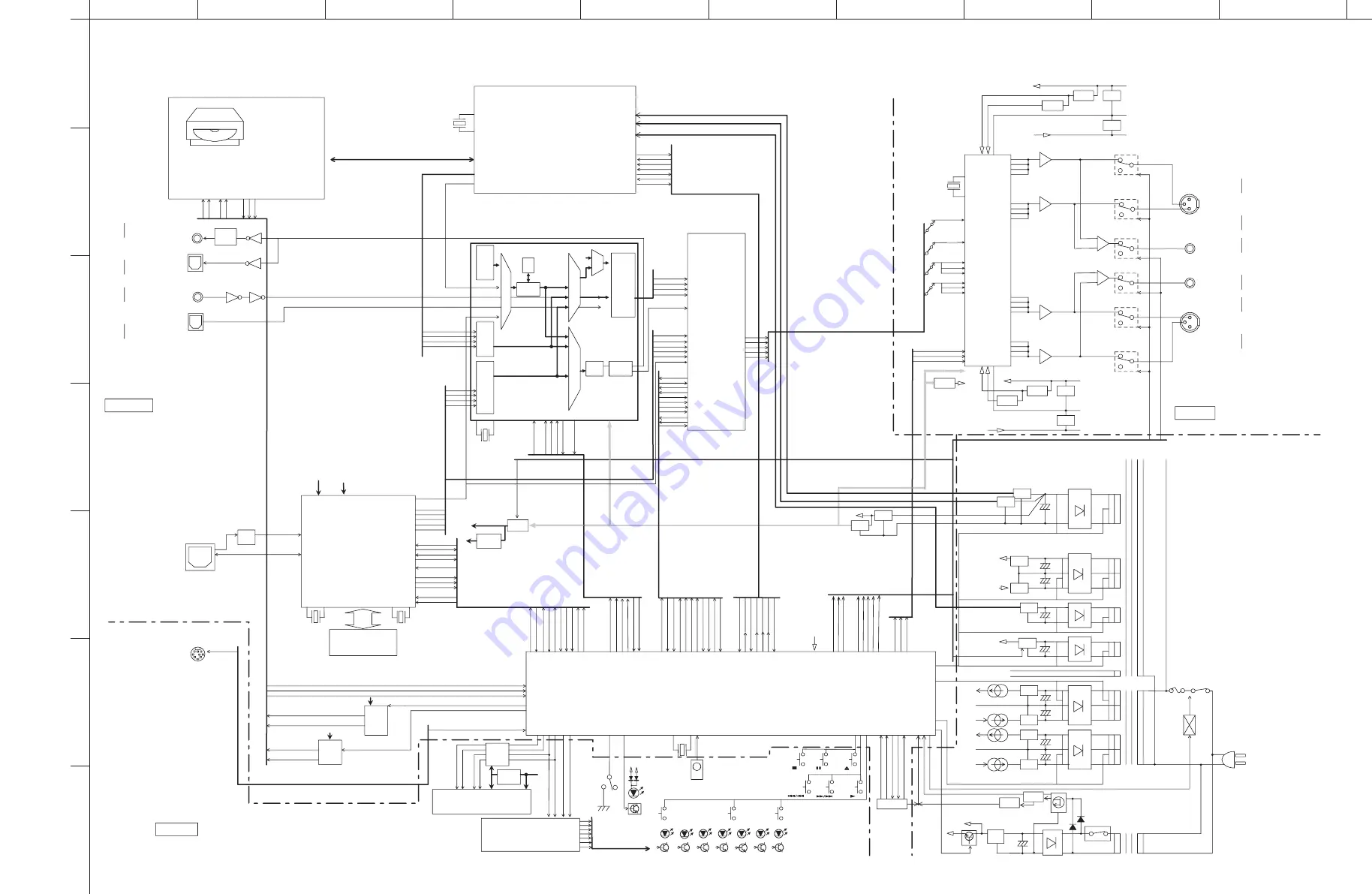

SA-CD

Module

Loader mechanism unit

+3.3USB

L

L

R

R

-12R

+12R

AGNDR

-12L

+12L

AGNDL

DIR_N_CS

DIR_SCK

DIR_MOSI

DIR MISO

26 : DIR_N_CS

25 : DIR_SCK

24 : DIR_MOSI

23 : DIR MISO

2 : DIR_N_INT

34 : DIR_N_RST

DIR_N_INT

DIR_N_RST

DAC_N_RST

DAC_SCL

DAC_N_RST

DAC_SCL

DAC_SCA

DAC_SCA

RY_BAL

RY_UNBAL

+3.3USB

+3.3D

+12RY

-12RY

+7MT

+30VP

FL1,2

COAXIAL

OPTICAL

COAXIAL

OPTICAL

DIGITAL

OUT

DIGITAL

IN

USB

DAC 3.3V

Shunt

Shunt

+12R

AGNDR

-12R

+3.3R

+1.2L

DAC 3.3V

DAC 1.2V

Shunt

Shunt

+12L

AGNDL

-12L

+3.3L

+1.2L

CD_YIVO

CD_YOVI

CD_RST

CD_SPDIF_RQ

CD_MUTE

CD_PWR

CD_PWR_DET

CD_YIVO

CD_YOVI

CD_MUTE

CD_PWR

CD_RST

CD_SPDIF_RQ

FL

FL_N_RST

APL_FL_EX_MOSI

APL_FL_EX_CLK

FL_N_CS

+30VP

LAYER

PURE

DIRECT

POWER

SSP2_YISO

SSP2_YOSI

Clamp

Motor

Driver IC

Tray

Motor

Driver IC

+8M

+8M

CLAMP_MTR1,2

TRAY_MTR1,2

TRAY_MTR1,2

CLAMP_MTR1,2

TRAY_MTR1,2

䋨

LOADING

䋩

CLAMP_MTR1,

Writing port

KEY1

KEY0

KEY0

LED_PWR

SW_PWR

REM

RXD0

TXD0

CTS

RTS

N_RESET

CNVSS

PRVD

PRVL

PRVR

N_RESET

ACPWR_DET

SYSTEM

CONNECTOR

SYS1_TXD,SYS1_RXD,

SYS1_RTS,SYS1_CTS

DOUT

PWR_RY

PWR_RY

SOURCE

LOAD+,LOAD-

CLAMP_SW, UNCLAMP_SW

TRAY_SW, TROPEN_SW, TRCLOSE_SW

LOAD+,LOAD-

CLAMP_SW, UNCLAMP_SW

TRAY_SW, TROPEN_SW, TRCLOSE_SW

LCO

3.3V

DP_USB_B

DM_USB_B

CD_PWR_DET

LED_SACD

IV Convertor

IV Convertor

+5MO1

+5D

+3.3D

RESET

PDET

+10S

+3.3M

+3.3S

+3.3M

STBY_CNT

+7MT

+5MO2

DAC 1.2V

+3.3D

SW

+3.3D

SSP2_PON

DAC 1.2V

DGND

CGND

MGND

+5MO1

+12D

FLGND

BCLK/DSDCL

WCK/DSDL

SDO/DSDL

FL_PON

I2SSEL_USB

RY_BAL

RY_UNBAL

I2SSEL_DSDPCM

FL_PON

SSP2_PON

USB_PON

LED_PDIRECT

+3.3

+3.3S

SEL_DIR_BYPASS

+3.3M

REG

+5V

Regulator

3.3V

㫋㫆㩷

5V

Convert

LED_CD

LED_DISC

LED_USB_DAC

LED_COAX

LED_OPT

APL_FL_EX_MOSI

APL_FL_EX_CLK

EX_N_IC

EX_N_CS

SSP2_MCK

SSP2_BCK

SSP2_WCK

SSP2_SDO0

SSP2_SDO1

SSP2_MCK

SSP2_BCK

SSP2_WCK

SSP2_SDO0

SSP2_SPDIF

PI_BCK_DSDCLK

PI_DSDR

PI_SDO_DSDL

PI_WCK

PI_BCK_DSDCLK

PI_DSDR

PI_SDO_DSDL

PI_WCK

SPDIF/DSDR

SDO/DSDR

DIR_BCK

DIR_WCK

DIR_SDO

DIR_MCK

SSP2_MCK

SSP2_BCK

SSP2_WCK

SSP2_SDO0

SSP2_SDO1

1.5V

Regulaotr

+1.5USB

+1.5USB

SSP2_YISO

SSP2_YOSI

SSP2_YISO_N_IRQ

SSP2_YOSI_N_IRQ

SSP2_YISO_N_IRQ

SSP2_YOSI_N_IR

SSP2_YOSI_MUTE

SSP2_YOSI_MUTE

SSP2_USB_RDY

SSP2_YISO_MUT

SSP2_YISO_DSD_PCM

SSP2_USB_RDY

SSP2_YISO_MUTE

SSP2_YISO_DSD_PCM

SSP2_N_IC

SSP2_N_DSPSTOP

SSP2_N_IC

SSP2_N_DSPSTOP

FPGA_INTN

FPGA_DSDMUTE

FPGA_DOP_DSDPCM

FPGA_DOP_DSDRATE

FPGA_PROG

FPGA_SEL_A

FPGA_SEL_B

FPGA_SEL_C

FPGA_DONE

SSP2_SPDIF

FPGA_RRESET

FPGA_JTAGEN

XL401

20MHz

13

15

XL1

40MHz

XL402

12.288MHz

XL404

30MHz

XL403

24.576MHz

Y101

27Hz

+5MO2

BALANCED

OUT

BALANCED

OUT

AC IN

ANALOG

OUT

39

40

RY3

RY3

RY1

RY2

RY4

RY4

R21

D1

R22

C1

24

POWER

TRANSFORMER

RY902

FRONT

• See page 66–68

→

SCHEMATIC DIAGRAM

DIGITAL

• See page 61–63

→

SCHEMATIC DIAGRAM

AUDIO

• See page 64, 65

→

SCHEMATIC DIAGRAM

A

B

C

D

E

F

G

H

I

J

1

2

3

4

5

6

7

CD-S3000

47

■

BLOCK DIAGRAM

Summary of Contents for CD-S3000

Page 6: ... FRONT PANELS U K A B G L V J models T model 6 CD S3000 CD S3000 ...

Page 7: ... REAR PANELS U V models U model V model Bottom view 7 CD S3000 CD S3000 ...

Page 8: ...A B G L models K model T model A model B G models 8 CD S3000 CD S3000 ...

Page 9: ...J model 9 CD S3000 CD S3000 ...

Page 86: ...86 CD S3000 CD S3000 ...

Page 87: ...MEMO 87 CD S3000 CD S3000 87 ...

Page 88: ...CD S3000 ...