CDR-HD1500

37

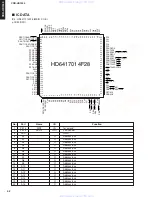

CDR-HD1500

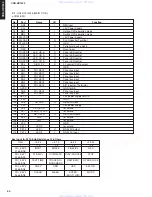

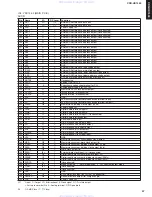

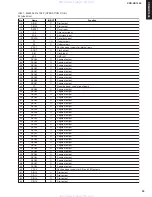

No.

Name

I/O

DC Level

Function

97

RD1

I/O

T/C

External RAM interface, data bus

98

RD0

I/O

T/C

External RAM interface, data bus

99

VDD

Power 5V

100

RA12

O

C

External RAM interface, address output (Unconnected)

101

RA11

O

C

External RAM interface, address output (Unconnected)

102

RA10

O

C

External RAM interface, address output (Unconnected)

103

RA9

O

C

External RAM interface, address output (Unconnected)

104

RA8

O

C

External RAM interface, address output

105

RA7

O

C

External RAM interface, address output

106

VSS

GND

107

RA6

O

C

External RAM interface, address output

108

RA5

O

C

External RAM interface, address output

109

RA4

O

C

External RAM interface, address output

110

RA3

O

C

External RAM interface, address output

111

RA2

O

C

External RAM interface, address output

112

RA1

O

C

External RAM interface, address output

113

RA0

O

C

External RAM interface, address output

114

VSS

GND

115

/ROE

O

C

External RAM interface, read strobe output

116

/RWE

O

C

External RAM interface, write strobe output

117

/RAS

O

C

External RAM interface, lower address strobe output

118

/CAS

O

C

External RAM interface column address strobe output

119

MUTSP

I

T

SPD pin mute control input, muting provided at “1”

120

MUTAE

I+

T

Unconnected

121

AVSS

Analog GND for PLL

122

PCO

A

Capacitance connection terminal for PLL

123

AVDD

Analog power supply for PLL +5V

124

/LOCK

O

C

Master clock, PLL lock detect output

125

/TESTA

I+

T

testing terminal (Unconnected)

126

/TESTB

I+

T

testing terminal (Unconnected)

127

VSS

GND

128

XI

I$

C

24.576MHz crystal oscillator connection terminal (input)

129

XO

O$

C

24.576MHz crystal oscillator connection terminal (output)

130

F256A

O$

C

Master clock, dividing clock output (256fs)

131

VDD

Power 5V

132

DINA

I+

T

Digital audio interface input A

133

DINB

I+

T

Digital audio interface input B

134

DINC

I+

T

Digital audio interface input C (Unconnected)

135

DOUT

O

C

Digital audio interface output

136

DDIN

I

T

Serial audio data input

137

SI

I+

T

DIR5 interface, control data input

138

SO

O

C

DIR5 interface, control data output

C

DIR5 interface, chip select output

C

DIR5 interface, bit clock output

T

DIR5 interface, interrupt input

T

DIR5 interface, U-bit signal input

GND

C

Master clock system, synchronous signal output

C

Master clock system, word clock output (fs)

C

Master clock system, dividing clock output (128fs)

C

Master clock system, dividing clock output (64fs)

C

Word clock output (fs)

T

External word clock input (fs) (Unconnected)

T

Digital input data system, word clock input (fs)

T

Digital input data system, dividing clock input (256fs)

152

F64B

I$

T

Digital input data system, dividing clock input (64fs)

153

SYNCC

I+

T

(Unconnected)

154

WCC

I$+

T

Mode switching, “1”: normal operation, “0”: PLL constant output mode

155

F128C

I$+

T

(Unconnected)

156

F64C

I$+

T

(Unconnected)

157

VSS

GND

158

DWCKI

I$

T

Drive word clock input (44.1kHz or 33.8688MHz)

159

DWCKO

O$

C

Drive word clock output (for charge couple)

160

VDD

Power 5V

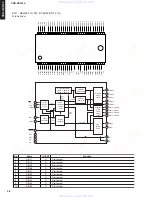

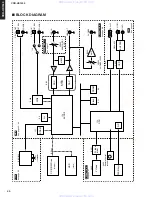

IC3 : YDC126-F (MAIN P.C.B.)

ACDR

I/O

I: Input O: Output I/O: Bi-directional $: Clock signal OT: Tri-state output

+: Pull-up resistor built-in A: Analog terminal OD: Open drain

DC

C: CMOS level T: TTL level

www. xiaoyu163. com

QQ 376315150

9

9

2

8

9

4

2

9

8

TEL 13942296513

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299