CDR-HD1500

A

1

2

3

4

5

6

7

8

9

B

C

D

E

G

H

I

J

K

L

46

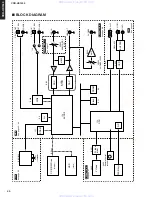

SCHEMATIC DIAGRAM (MAIN 2/2)

AK4528VF

1

14

28

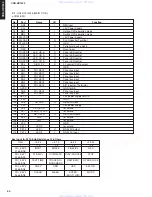

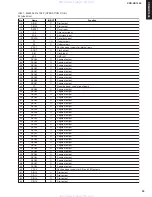

2SC2412K

2SD1938F

DTC114EKA

DTA143EK

1SS355

MA732

MA8051-M

PIN CONNECTION DIAGRAM OF TRANSISTORS,

DIODES AND ICS.

B

E

C

Anode

Cathode

SN74LS06NST-EL

1

7

14

PST572CMT-R

NJM2100M

NJM2904M

NJM4580E

2

1

3

MBM29F800BA-70PFTN

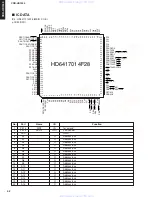

HD6417014F28

1

40

41

80

81

120

121

160

YDC126-F

MSM5118160F-60JSR1

1

28

29

56

57

84

85

112

HD74HC02FPEL

TC74HC14AF

TC74HCU04AFEL

TC4052BF

TC9246F-TEL

1

7

14

1

8

16

1

24

25

48

1

4

8

YSD917

1

14

28

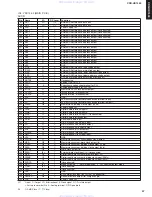

IC201: HD74HC02FPEL

Quad 2 Input NOR

1

2

3

4

5

6

7

14

13

12

11

10

9

8

Y1

A1

B1

Y2

A2

B2

GND

VCC

Y4

B4

A4

Y3

B3

A3

IC200: TC74HCU04AFEL

Hex Inverters

1A

1Y

2Y

VCC

6A

1

2

3

4

11

2A

6Y

5A

12

13

14

3A

3Y

5Y

4A

5

6

7

4Y

8

9

10

GND

IC202: NJM2904M

Dual OP-Amp

Q1

Q2

Q3

Q9

Q8

Q4

INPUTS

OUTPUT

V–

–

+

Q6

Q5

Q10

Q11

Q12

Q7

Q13

IC203~204: NJM2100M

Dual OP-Amp

8

2, 6

3, 5

1, 7

4

V+

–INPUT

+INPUT

V–

OUTPUT

V+

–INPUT

+INPUT

V–

OUTPUT

IC205: NJM4580E

Dual OP-Amp

8

2, 6

3, 5

1, 7

4

IC206: TC4052BF

Analog Multiplexers/Demultiplexers

16

10

9

6

8

7

13

12

14

15

11

1

5

2

4

3

X-COMMON

0X

1X

2X

3X

0Y

1Y

2Y

3Y

Y-COMMON

VEE

VSS

INH

B

A

VDD

LOGIC LEVEL

CONVER

TER

I/O c O/I

I/O c O/I

I/O c O/I

I/O c O/I

I/O c O/I

I/O c O/I

I/O c O/I

I/O c O/I

IC208: YSD917

DIR

IC210: AK4528VF

24bit CODEC

ADC

AINL+

20

DEM0

21

DEM1

HPF

Audio

I/F

Controller

AINL-

23

VD

22

VT

24

DGND

19

PDN

11

LRCK

12

BICK

13

SDTO

14

SDTI

4

5

AINR+

AINR-

2

VREF

VA

6

8

AGND

7

3

ADC

AOUTL+

HPF

Control Register I/F

AOUTL-

26

VCOM

1

25

AOUTR+

P/S

28

AOUTR-

27

9

CCLK

(CKS1)

16

CSN

(DIF)

17

CDTI

(CKS0)

15

Clock Divider

MCLK

10

DFS

18

Digital audio interface decoder &

lock error judgment

16

SDMCK

13

SDO

20

DBL/V

21

ERR/BS

18

SYNC/U

19

FS128/C

14

SDBCK

15

SDWCK

5

DDIN

7

/IC

AVDD

PCO

AVSS

M/S

DDIN

TEST

/IC

VSS

XO

XI

MCK

VDD

SDO

SDBCK

1

2

3

4

5

6

7

8

9

10

11

12

13

14

SCK

SI

SO

/CS

VDD

INT

/LOCK

ERR/BS

DBL/V

FS128/C

SYNC/U

VSS

SDMCK

SDWCK

28

27

26

25

24

23

22

21

20

19

18

17

16

15

2

PLL

Each control signal

DATA BUS

Output

selection

Clock

system

selection

Output

clock

generation

Flame

Buffer

Serial

Converter

Channel Status

User Data

Microprocessor

interface

22

/LOCK

PCO

9

Reference

clock

generation

XO

11

MCK

10

XI

4

M/S

26

SO

Interrupt factor

detection

23

INT

27

SI

28

SCK

25

/CS

★

All voltage are measured with a 10M

Ω

/V DC electric volt meter.

★

Components having special characteristics are marked

s

and must be replaced

with parts having specifications equal to those originally installed.

★

Schematic diagram is subject to change without notice.

DIGITAL

OUT

DIGITAL

IN

DIR

24 BIT

CODEC

BUFFER

MIXER

MUTE

LPF

ANALOG L / R

IN

ANALOG L / R

OUT

3

4

6

5

4

7

1

2

3

8

3

2

4

5

6

2

5

1

13

11

15

14

12

4

3

6

7

14

1

2

8

5

6

7

14

3

1

7

8

4

6

5

9

8

11

10

13

1

21

42

Page 47

to OPERATION (1)

H7

Page 48

to OPERATION (4)

I8

P

age 49

to OSD

A6

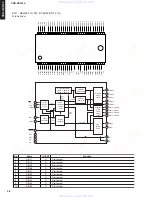

1

20

40

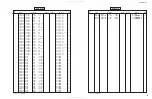

GLT44016

0

0

2.6

0

2.6

2.6

5.1

0

0

0

-5.0

0

0

0

-4.9

-4.9

0

0

-4.9

-4.9

0

0

-4.9

0

0

-4.9

0

0

-4.9

0

-4.7

0

2.6

5.1

2.6

2.6

2.6

0

2.6

2.6

2.6

5.1

2.6

2.6

0

0

0

0

0

0

0

0

0

0

5.1

0

5.1

5.1

5.1

0

0

0

5.1

5.1

0

4.9

4.9

0

2.5

2.6

2.5

2.5

1.3

~

2.5

2.5

2.4

0

5.1

0

5.1

2.6

2.6

2.6

2.6

2.5

5.1

3.4

3.4

5.1

0

0

5.1

0

2.6

2.4

5.1

0

2.5

2.5

0

5.1

5.1

5.1

5.1

0

5.1

0

0

0

2.5

2.5

2.5

2.5

4.0

5.1

0

0

0

0

0

0

0

5.1

5.1

0

5.1

0

0

5.1

0

0

5.1

0

0.1

2.7

2.7

2.7

2.7

0

0

3.0

2.5

5.1

0

2.7

5.1

0

5.1

0

4.0

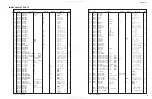

ANALOG OUT

(DIGITAL)

ANALOG OUT

OPTICAL

COAXIAL

OPTICAL

COAXIAL

w w w

.

x i a o y

u 1 6 3 .

c o m

Q Q

3 7 6 3 1 5 1 5 0

9

9

2

8

9

4

2

9

8

T E L

1 3 9 4 2 2 9 6 5 1 3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299