16

CLP-110

■

IC BLOCK DIAGRAM

●

YMZ702-D (XR632A00) KSN2 (Key Scanner)

PIN

PIN

NO.

NAME

I/O

FUNCTION

NO.

NAME

I/O

FUNCTION

1

BK5

O

21

GND

Ground

2

BK4

O

22

VDD

Power supply

3

BK3

O

Key block (open drein)

23

SO

O

Serial data

4

BK2

O

24

ACK

I

Acknowledge/mode select

5

BK1

O

25

XCK

I

Clock for serial data

6

BK0

O

26

/IC

I

Initial clear

7

MK15

I

27

TST1

I

Test mode

8

MK14

I

28

TST2

I

(L,L: normal mode, others: test)

9

MK13

I

First make contact

29

XCKINH

I

Inhibit of serial clock

10

MK12

I

30

BK14

O

11

MK11

I

31

BK13

O

12

MK10

I

32

BK12

O

13

MK05

I

33

BK11

O

14

MK04

I

34

BK10

O

Key block (open drein)

15

MK03

I

Second make contact

35

BK9

O

16

MK02

I

36

BK8

O

17

MK01

I

37

BK7

O

18

MK00

I

38

BK6

O

19

XIN

I

Crystal osc. input (4 MHz)

39

GND

Ground

20

XOUT

O

Crystal osc. output (4 MHz)

40

VDD

Power supply

●

UPD63200GS-E1 (XP867A00) DAC (Digital to Analog Converter)

PIN

PIN

NO.

NAME

I/O

FUNCTION

NO.

NAME

I/O

FUNCTION

1

4/8

I

4/8 Fs selection

9

R.REF

Channel R voltage reference

2

D.GND

Digital ground

10

L.REF

Channel L voltage reference

3

16 BIT

I

16bit/18bit selection

11

L.OUT

O

Channel L output

4

D.GND

Digital power supply

12

A.GND

I

Analog ground

5

A,GND

Analog ground

19

WDCK

I

Word clock

6

R.OUT

O

Channel R output

20

RSI

I

Channel R series input

7

A.VDD

Analog power supply

21

SI/LSI

I

Series input/Channel L series input

8

A.VDD

22

CLK

I

Clock

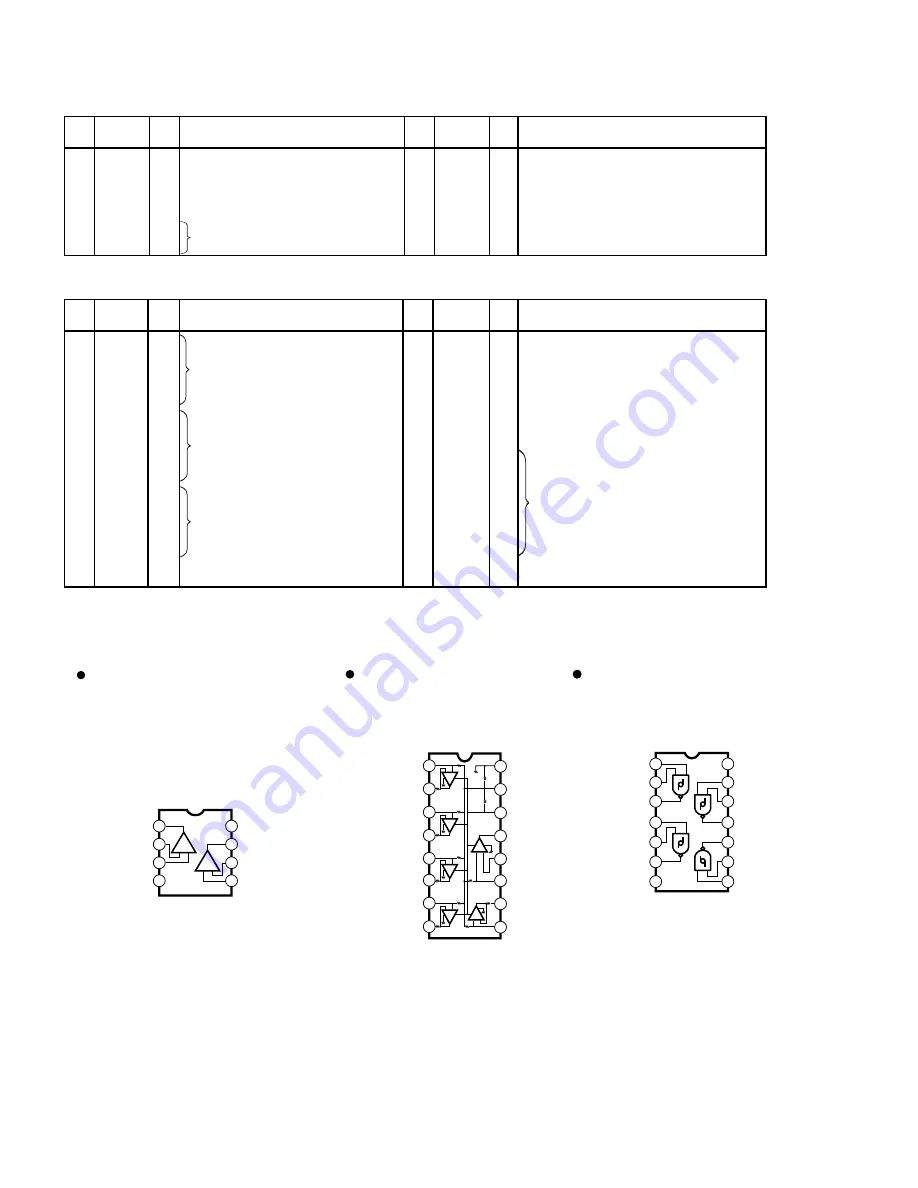

µPC4570G2 (XF291A00)

Dual Operational Amplifier

AM: IC007

1

2

3

4 -V

8

7

6

5

Output A

+V

Non-Inverting

Input A

-DC Voltage Supply

+DC Voltage

Supply

Output B

Inverting

Input B

Non-Inverting

Input B

Inverting

Input A

+

-

+ -

M5227FP (XT773A00)

Graphic Equalizer

1

2

3

4

5

6

7

IN1

NF1

IN2

NF2

IN3

NF3

IN4

16

15

14

13

12

11

10

-Vcc

GND

+Vcc

OUT

-IN

10k

10k

47k

47k

47k

540

540

540

540

540

540

47k

47k

47k

+IN

NF5

8

NF4

9

IN5

+-

+-

+-

+-

+ -

+ -

1

2

3

1A

1Y

4

2Y

5

2A

6

2B

7

GND

1B

14

13

12

VDD

4A

11

4Y

10

3Y

9

3B

8

3A

4B

SN74HC132NSR (XW792A00)

MM74HC132SJX (XY352A00)

Quad 2 Input NAND