15

DTX-MULTI 12

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

209

210

212

213

214

215

216

217

218

219

220

221

222

223

224

225

226

227

228

229

230

231

232

233

234

235

236

237

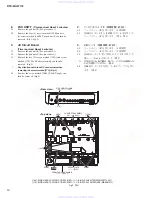

L1

L2

L3

L4

L5

L9

L10

L11

L12

L16

L17

L18

L19

L20

M1

M2

M3

M4

M5

M9

M10

M11

M12

M16

M17

M18

M19

M20

N1

N2

N3

N4

N5

N16

N17

N18

N19

N20

P1

P2

P3

P4

P5

P16

P17

P18

P19

P20

R1

R2

R3

R4

R5

T10

T11

T12

T13

T14

T15

T16

T17

T18

T19

T20

U1

MA15

MA16

MA17

MA18

VDD

VSS

VSS

VSS

VSS

VDD

D11

D12

D13

D14

MA19

MA20

MA21

MA22

VSS

VSS

VSS

VSS

VSS

VSS

D7

D8

D9

D10

MA23/PG4

MA24/PG5

MA25/PG6

MA26/PG7

VCCQ

VCCQ

D3

D4

D5

D6

MCS3N/PG3

MCS2N/PG2

MCS1N/PG1

MWRN/PG0

VSS

VSS

RD/WRN

D0

D1

D2

MCS0N

VCCQ

VCCQ

VSS

VCCQ

VSS

VDD

VDD

A0/PH4

WE0N/DQMLL/PH0

WE1N/DQMLU/PH1

WE2N/DQMUL/PH2

PA5

O

O

O

O

-

-

-

-

-

-

I/O

I/O

I/O

I/O

O

O

O

O

-

-

-

-

-

-

I/O

I/O

I/O

I/O

O

O

O

O

-

-

I/O

I/O

I/O

I/O

O

O

O

O

-

-

O

I/O

I/O

I/O

O

O

-

-

-

-

-

-

-

-

-

-

-

-

O

O

O

O

I/O

Wave memory address bus 15

Wave memory address bus 16

Wave memory address bus 17

Wave memory address bus 18

Power 1.2 V

Ground

Power 1.2 V

SH2A-CPU data bus 11

SH2A-CPU data bus 12

SH2A-CPU data bus 13

SH2A-CPU data bus 14

Wave memory address bus 19

Wave memory address bus 20

Wave memory address bus 21

Wave memory address bus 22

Ground

SH2A-CPU data bus 7

SH2A-CPU data bus 8

SH2A-CPU data bus 9

SH2A-CPU data bus 10

Wave memory address bus 23

Wave memory address bus 24

Wave memory address bus 25

Wave memory address bus 26

Power 3.3 V

SH2A-CPU data bus 3

SH2A-CPU data bus 4

SH2A-CPU data bus 5

SH2A-CPU data bus 6

Wave memory chip select 3

Wave memory chip select 2

Wave memory chip select 1

Wave memory write enable

Ground

SH2A-CPU read/write enable

SH2A-CPU data bus 0

SH2A-CPU data bus 1

SH2A-CPU data bus 2

Wave memory chip select 0

Wave memory read enable

BOOT ROM switching control

Parallel port A0

Power 1.2 V

Writing byte of D31 - D24/Selecting D31 - D24 in case of SDRAM

RAS output for SDRAM

CAS output for SDRAM

SH2A-CPU read enable

Parallel port A1

Parallel port A2

Parallel port A3

Parallel port A4

Power 1.2 V

Ground

Power 3.3 V

Ground

Power 3.3 V

Ground

Power 3.3 V

Ground

Power 1.2 V

SH2A-CPU address bus 0

Writing byte of D7 - D0/Selecting D7 - D0 in case of SDRAM

Writing byte of D15 - D8/Selecting D15 - D8 in case of SDRAM

Writing byte of D23 - D16/Selecting D23 - D16 in case of SDRAM

Parallel port A5

238

239

240

241

242

243

244

245

246

247

248

249

250

251

252

253

254

255

256

257

258

259

260

261

262

263

264

265

266

267

268

269

270

271

272

273

274

275

276

277

278

279

280

281

282

283

284

285

286

287

288

289

290

291

292

293

294

295

296

297

298

299

300

301

302

303

304

305

306

307

308

309

310

311

312

313

314

315

316

U2

U3

U4

U5

U6

U7

U8

U9

U10

U11

U12

U13

U14

U15

U16

U17

U18

U19

U20

V1

V2

V3

V4

V5

V6

V7

V8

V9

V10

V11

V12

V13

V14

V15

V16

V17

V18

V19

V20

W1

W2

W3

W4

W5

W6

W7

W8

W9

W10

W11

W12

W13

W14

W15

W16

W17

W18

W19

W20

Y1

Y2

Y3

Y4

Y5

Y6

Y7

Y8

Y9

Y10

Y11

Y12

Y13

Y14

Y15

Y16

Y17

Y18

Y19

Y20

PA6

PA7

VCCQ

ED1/PC1

ED5/PC5

ED9/PD1

ED13/PD5

EA2/PK1

ECSN

BCLK

IRQ0

A25

A21

A17

A13

VCCQ

A3

A2

A1

PB0

PB1

VCCQ

PB6

ED2/PC2

ED6/PC6

ED10/PD2

ED14/PD6

EA3/PK2

SDI0/PK5

WCLK2/SDO2

IRQ1

BW_MD0

A22/PH5

A18

A14

A10

VCCQ

A5

A4

PB2

VCCQ

PB4

PB7

ED3/PC3

ED7/PC7

ED11/PD3

ED15/PD7

ERDN/PK3

SDI1/PK6

WCLK

SYSCLK2

WAITN/PK7

A23/PH6

A19

A15

A11

A8

VCCQ

A6

VCCQ

PB3

PB5

ED0/PC0

ED4/PC4

ED8/PD0

ED12/PD4

EA1/PK0

EWRN/PK4

SDO0

SDO1

SYSCLK

SYI

A24/PH7

A20

A16

A12

A9

A7

VCCQ

I/O

I/O

-

I/O

I/O

I/O

I/O

I

I

O

I

O

O

O

O

-

O

O

O

I/O

I/O

-

I/O

I/O

I/O

I/O

I/O

I

I

O

I

I

O

O

O

O

-

O

O

I/O

-

I/O

I/O

I/O

I/O

I/O

I/O

I

I

O

O

I

O

O

O

O

O

-

O

-

I/O

I/O

I/O

I/O

I/O

I/O

I

I

O

O

O

I

O

O

O

O

O

O

-

Parallel port A6

Parallel port A7

Power 3.3 V

External CPU data bus 1

External CPU data bus 5

External CPU data bus 9

External CPU data bus 13

External CPU address bus 2

External CPU chip select

Bit clock output

Interrupt input 0

SH2A-CPU address bus 25

SH2A-CPU address bus 21

SH2A-CPU address bus 17

SH2A-CPU address bus 13

Power 3.3 V

SH2A-CPU address bus 3

SH2A-CPU address bus 2

SH2A-CPU address bus 1

Parallel port B0

Parallel port B1

Power 3.3 V

Parallel port B6

External CPU data bus 2

External CPU data bus 6

External CPU data bus 10

External CPU data bus 14

External CPU address bus 3

Serial audio input 0

Word clock output 2/Serial audio output 2

Interrupt input 1

SH2A-CPU data bus width configuration

SH2A-CPU address bus 22

SH2A-CPU address bus 18

SH2A-CPU address bus 14

SH2A-CPU address bus 10

Power 3.3 V

SH2A-CPU address bus 5

SH2A-CPU address bus 4

Parallel port B2

Power 3.3 V

Parallel port B4

Parallel port B7

External CPU data bus 3

External CPU data bus 7

External CPU data bus 11

External CPU data bus 15

External CPU read enable

Serial audio input 1

Word clock output

Clock output 2

External wait input

SH2A-CPU address bus 23

SH2A-CPU address bus 19

SH2A-CPU address bus 15

SH2A-CPU address bus 11

SH2A-CPU address bus 8

Power 3.3 V

SH2A-CPU address bus 6

Power 3.3 V

Parallel port B3

Parallel port B5

External CPU data bus 0

External CPU data bus 4

External CPU data bus 8

External CPU data bus 12

External CPU address bus 1

External CPU write enable

Serial audio output 0

Serial audio output 1

Clock output

Sync. input from external device

SH2A-CPU address bus 24

SH2A-CPU address bus 20

SH2A-CPU address bus 16

SH2A-CPU address bus 12

SH2A-CPU address bus 9

SH2A-CPU address bus 7

Power 3.3 V

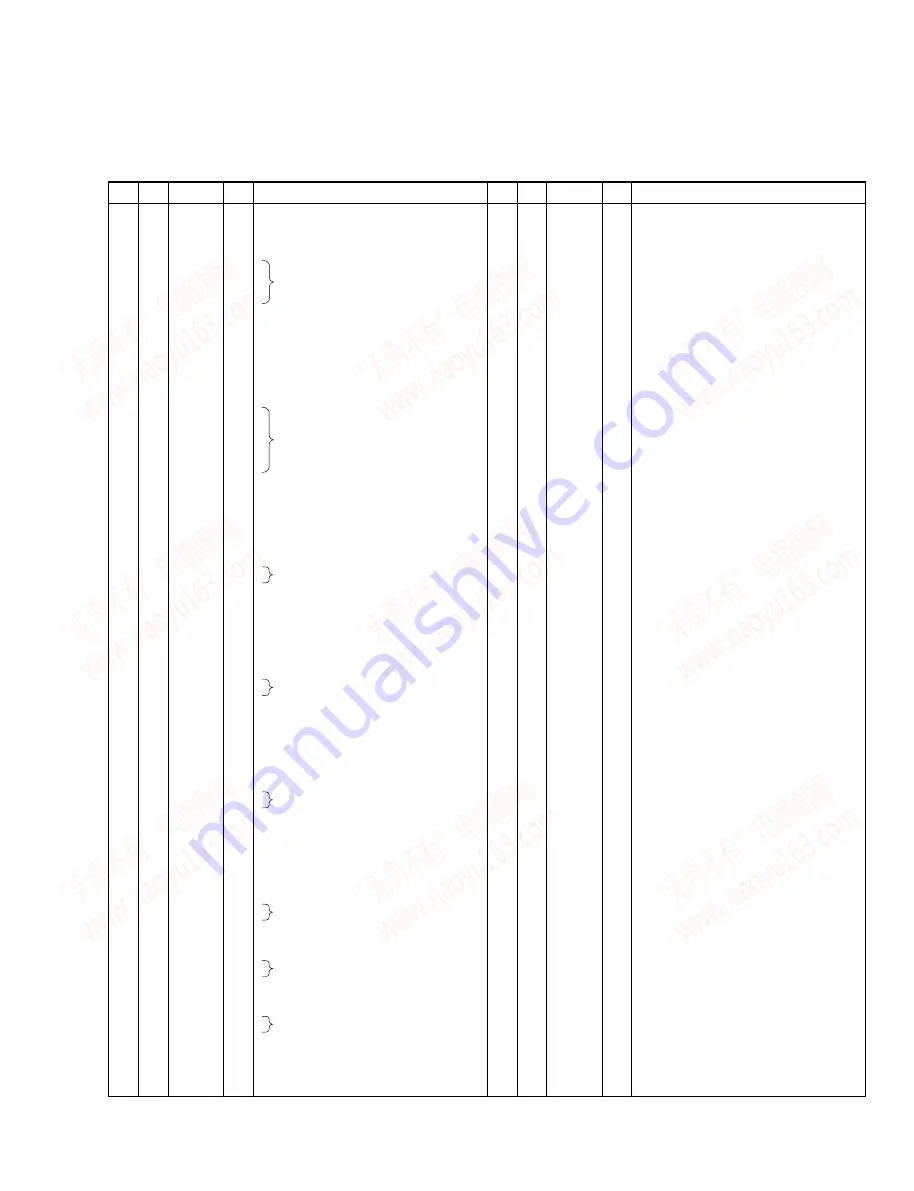

PIN

NO.

OUTER

NO.

NAME

I/O

FUNCTION

PIN

NO.

OUTER

NO.

NAME

I/O

FUNCTION

www. xiaoyu163. com

QQ 376315150

9

9

2

8

9

4

2

9

8

TEL 13942296513

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299