62

RX-V381/HTR-3069

RX-V381/HTR-3069

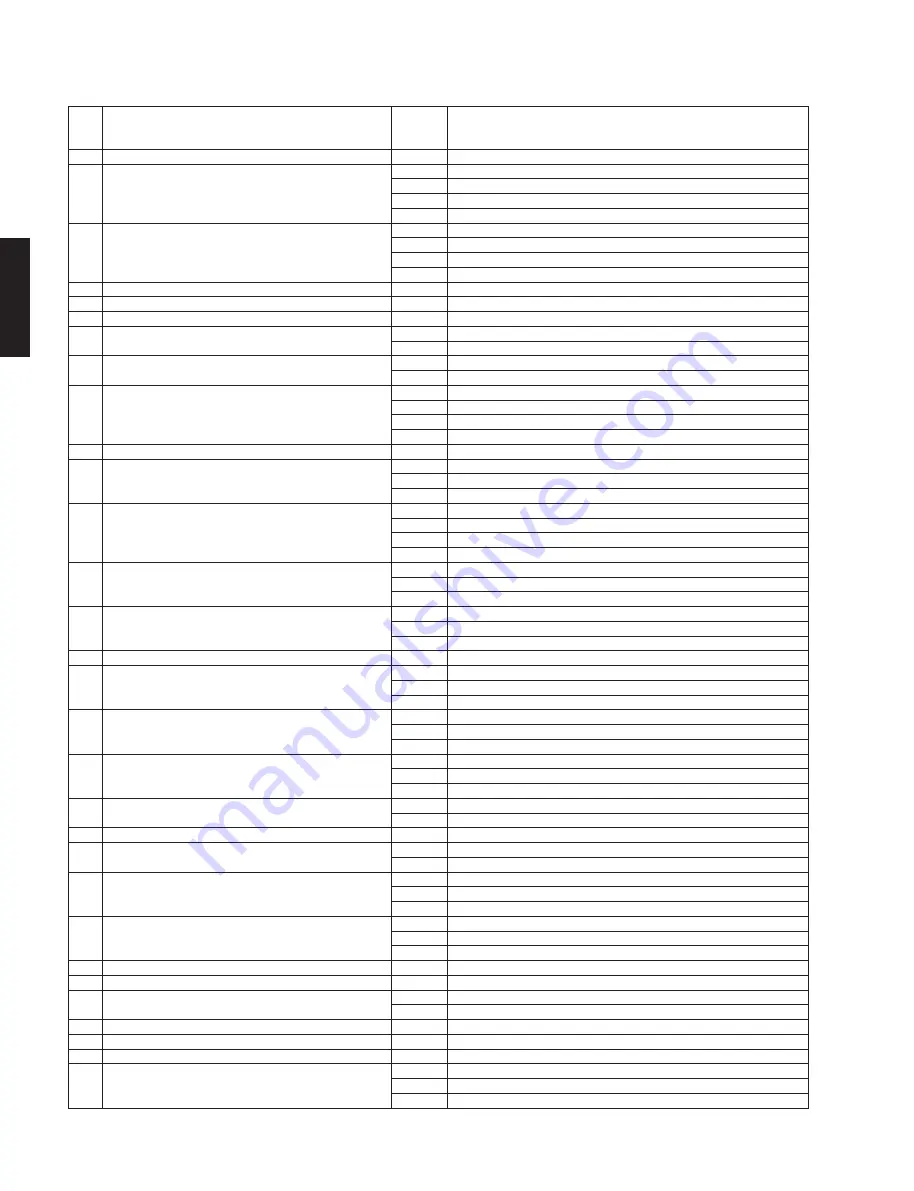

No.

Function Name

(P.C.B.)

I/O

Detail of Function

1

AXR1[0

]

/GP4[0

]

I/O

McASP1serial data

2

UART0_RXD/I2C0_SDA/TM

6

4P0_IN12/GP

5

[

8]

/BOOT[

8]

I

UART0 receive data

I/O

I2C0 serial data

I

Timer0 lower input

I

BOOT[

8]

3

UART0_TXD/I2C0_SCL/TM

6

4P0_OUT12/GP

5

[

9]

/BOOT[

9]

O

UART0 transmit data

I/O

I2C0 serial clock

I

Timer0 lower output

I

BOOT[

9]

4

AXR1[10

]

/GP

5

[10

]

I/O

McASP1serial data

5

DVDD

6

AXR1[11

]

/GP

5

[11

]

I/O

McASP1serial data

7

SPI1_ENA/UART2_RXD/GP

5

[12

]

I/O

SPI1enable

I

UART2 receive data

8

SPI1_SCS[0

]

/UART2_TXD/GP

5

[1

3]

I/O

SPI1 chip select

O

UART2 transmit data

9

SPI0_SCS[0

]

/ UART0_RTS /EQEP0B/GP

5

[4

]

/BOOT[4

]

I/O

SPI0 chip select

O

UART0 ready-to-send output

I

eQEP0B quadrature input

I

BOOT[4

]

10

CVDD

11

SPI0_CL

K

/EQEP1I/GP

5

[2

]

/BOOT[2

]

I/O

SPI0 clock

I

eQEP1 index

I

BOOT[2

]

12

SPI0_ENA/ UART0_CTS /EQEP0A/GP

5

[

3]

/BOOT[

3]

I/O

SPI0 enable

I

UART0 clear-to-send input

I

eQEP0A quadrature input

I

BOOT[

3]

1

3

SPI1_SOMI[0

]

/I2C1_SCL/GP

5

[

5]

/BOOT[

5]

I/O

SPI1 data slave-out-master-in

I/O

I2C1 serial clock

I

BOOT[

5]

14

SPI1_SIMO[0

]

/I2C1_SDA/GP

5

[

6]

/BOOT[

6]

I/O

SPI1 data slave-in-master-out

I/O

I2C1 serial data

I

BOOT[

6]

1

5

DVDD

1

6

SPI1_CL

K

/EQEP1S/GP

5

[7

]

/BOOT[7

]

I/O

SPI1 clock

I

eQEP1 strobe

I

BOOT[7

]

17

SPI0_SOMI[0

]

/EQEP0I/GP

5

[0

]

/BOOT[0

]

I/O

SPI0 data slave-out-master-in

I

eQEP0 index

I

BOOT[0

]

1

8

SPI0_SIMO[0

]

/EQEP0S/GP

5

[1

]

/BOOT[1

]

I/O

SPI0 data slave-in-master-out

I

eQEP0 strobe

I

BOOT[1

]

1

9

EMA_WAIT[0

]

/ U

H

PI_

H

RDY /GP2[10

]

I

EMIFA wait input/interrupt

I/O

U

H

PI ready

20

CVDD

21

EMA_CS[

3]

/AMUTE2/GP2[

6]

O

EMIFA Async chip select

I/O

McASP2 mute output

22

EMA_OE/U

H

PI_

H

DS1/AXR0[1

3]

/GP2[7

]

O

EMIFA output enable

I/O

U

H

PI data strobe

I/O

McASP0 serial data

2

3

EMA_CS[2

]

/ U

H

PI_

H

CS /GP2[

5]

/BOOT[1

5]

O

EMIFA Async chip select

I/O

U

H

PI chip select

I

BOOT[1

5]

24

DVDD

2

5

EMA_BA[0

]

/ GP1[14

]

O

EMIFA bank address

2

6

EMA_BA[1

]

/ U

H

PI_

HH

WIL / GP1[1

3]

O

EMIFA bank address

I/O

U

H

PI half-word identification control

27

EMA_A[10

]

/ GP1[10

]

O

EMIFA address bus

2

8

CVDD

2

9

EMA_A[0

]

/ GP1[0

]

O

EMIFA address bus

3

0

EMA_A[1

]

/ MMCSD_CL

K

/ U

H

PI_

H

CNTL0 / GP1[1

]

O

EMIFA address bus

O

MMCSD_CL

K

I/O

U

H

PI access control

Summary of Contents for HTR-3069

Page 6: ...6 RX V381 HTR 3069 RX V381 HTR 3069 RX V381 K model RX V381 A model RX V381 B model ...

Page 7: ...7 RX V381 HTR 3069 RX V381 HTR 3069 RX V381 G F models RX V381 L model RX V381 S model ...

Page 8: ...8 RX V381 HTR 3069 RX V381 HTR 3069 RX V381 J model HTR 3069 U C models HTR 3069 T model ...

Page 9: ...9 RX V381 HTR 3069 RX V381 HTR 3069 HTR 3069 K model HTR 3069 B model TR 3069 G F models ...

Page 10: ...10 RX V381 HTR 3069 RX V381 HTR 3069 HTR 3069 L model ...

Page 138: ...RX V379 HTR 3068 ...