A

1

2

3

4

5

6

7

8

9

10

K

J

I

H

G

F

E

D

C

B

L

N

M

91

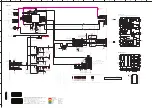

RX-V381/HTR-3069

A/D IN

EMA

9

E M D Q M 1

AUP_BCK

DSP_N_RD

Y

T I _ S D S B

EMA

1

D I R _ S D O

/EMRA

S

E M A 9

E M C L K

E M B A 0

AUP_WCK

DSP_N_CS

AUP_SD0

E M D 4

H D M I _ W C K / D L 2

T M S

N _ T R S T

D I R _ W C K

E M D 5

D S P _ N _ R S T

TI_SD

F

TI_SDSB

H D M I _ D R 2

T D O

TI_SD

S

T D O

T C K

E M D 1 3

E M A 1 1

SFL_N_CSSFL_N_CS

T D I

D I R _ M C K 1

E M D 1 2

E M D 6

E M A 0

D I R _ B C K

E M D 0

E M D 7

E M D 0

D S P _ S C K

E M A 6

E M D 1 5

E M D 3

EMA

8

D S P _ M O S I

E M B A 1

E M D 1 4

E M D 2

E M A 2

EMA

7

D S P _ M I S O

E M A 5

E M D 1 3

E M D 1

EMA

6

D S P _ N _ R D Y

E M D 7

T I _ W C K

E M D 1 2

D I R _ S D O

EMA

5

D S P _ N _ C S

D S P _ N _ R S T

E M C K E

EMA

4

E M D Q M 0

T C K

E M D 1

EMA

0

H D M I _ S D 3 / D R 0 / S P F

E M D 4

E M D Q M 1

H D M I _ S D 2 / D L 1

/ E M W E

DSP_N_IN

T

E M D 3

EMBA

1

/ E M W E

E M C L K

H D M I _ S D 1 / D R 1

/ E M C A S

DSP_FM

T

E M D 2

E M A 7

E M D Q M 0

E M A 1

EMBA

0

D S P _ F M T

E M D 1 0

E M D 6

/ E M R A S

E M A 4

T D I

E M D 9

/ E M C S

A U P _ B C K

E M D 8

T M S

/ E M C A S

D S P _ N _ I N T

A U P _ W C K

E M D 1 5

TI_SD

C

E M D 1 1

DSP_SC

K

DSP_SC

K

E M D 5

D I R _ W C K

E M D 1 4

E M D 1 1

E M A 3

T I _ B C K

A U P _ S D 0

EMA1

0

TI_BC

K

E M D 1 0

T I _ S D F

E M A 8

DSP_MISO

E M D 9

EMA

3

E M A 1 0

EMA1

1

DSP_MOSI

TI_WC

K

E M D 8

N _ T R S T

T I _ S D S

EMA

2

/EMC

S

DIR_MCK

1

H D M I _ S D 1 / D R 1

H D M I _ S D 2 / D L 1

H D M I _ S D 3 / D R 0 / S P F

H D M I _ D R 2

T I _ S D C

E M C K E

SFL_CL

K

SFL_DO

D I R _ B C K

SFL_DI

R 2 4 0 2

1 0 0 K

R 2 4 2 2

1 0 K

A U P _ S D 0

C 2 4 5 0

0 . 1 / 1 0 ( B J )

C 2 4 1 2

0 . 1 / 1 0 ( B J )

C241

9

no_us

e

C 2 4 0 4

1 8 P ( C H )

C242

6

0.1/10(BJ)

D S P _ N _ C S

H D M I _ S D 1 / D R 1

C 2 4 5 2

0 . 1 / 1 0 ( B J )

T I _ B C K

R242

3

10

K

C242

2

0.1/10(BJ

)

C243

4

0.1/10(BJ

)

R243

9

47X

4

D G N D

C247

1

0.1/10(BJ

)

C 2 4 1 3

0 . 1 / 1 0 ( B J )

C 2 4 5 5

0 . 1 / 1 0 ( B J )

D G N D

R242

5

10

K

D S P _ M I S O

C 2 4 1 5

0 . 1 / 1 0 ( B J )

C242

5

0.1/10(BJ

)

R 2 4 4 5

4 7 X 4

R 2 4 4 4

4 7 X 4

D S P _ N _ R S T

C243

2

0.1/10(BJ)

C 2 4 1 1

0 . 1 / 1 0 ( B J )

D I R _ M C K 1

D I R _ S D O

C 2 4 4 9

0 . 1 / 1 0 ( B J )

T I _ S D F

R 2 4 1 3

1 0 K

C244

1

0.1/10(BJ

)

D G N D

R243

6

150X

4

C 2 4 0 9

0 . 1 / 1 0 ( B J )

C242

8

0.1/10(BJ

)

D S P _ N _ I N T

C 2 4 0 8

0 . 1 / 1 0 ( B J )

D S P _ M O S I

C 2 4 1 0

0 . 1 / 1 0 ( B J )

D I R _ W C K

C 2 4 5 8

0 . 1 / 1 0 ( B J )

C 2 4 5 7

0 . 1 / 1 0 ( B J )

C242

7

0.1/10(BJ)

C242

4

0.1/10(BJ)

R 2 4 0 9

n o _ u s e

D S P _ N _ R D Y

R 2 4 4 3

4 7 X 4

C 2 4 2 1

n o _ u s e

C244

4

no_us

e

C 2 4 5 9

0 . 1 / 1 0 ( B J )

R241

8

33

R241

5

10

0

C 2 4 4 7

0 . 1 / 1 0 ( B J )

C 2 4 6 8

0 . 1 / 1 0 ( B J )

A U P _ B C K

L 2 4 0 2

B K P 1 0 0 5 H S 6 8 0 - T

R 2 4 0 1

1 0 0

R 2 4 2 8

4 . 7 K

C 2 4 1 6

0 . 1 / 1 0 ( B J )

C2466

0.1/10(BJ

)

C 2 4 4 3

n o _ u s e

C247

0

0.1/10(BJ

)

D S P _ S C K

C244

5

no_use

0

J 2 4 0 2

C 2 4 3 9

n o _ u s e

T I _ W C K

C240

3

470P(B)

H D M I _ D R 2

D G N D

R241

7

33

L240

3

BLM21PG600SN1D

H D M I _ S D 3 / D R 0 / S P F

C 2 4 5 6

0 . 1 / 1 0 ( B J )

R241

6

no_use

R 2 4 4 2

4 7 X 4

+ 3 . 3 D S P 1

R243

7

47X4

C 2 4 1 4

0 . 1 / 1 0 ( B J )

C 2 4 5 1

0 . 1 / 1 0 ( B J )

C243

3

0.1/10(BJ)

C243

5

0.1/10(BJ)

C243

6

0.1/10(BJ

)

C243

1

0.1/10(BJ

)

R240

8

4.7K

L240

4

BKP1005HS680-T

H D M I _ S D 2 / D L 1

R 2 4 4 1

4 7 X 4

R244

0

47X4

C 2 4 0 7

0 . 0 1 / 1 6 ( B )

C 2 4 4 8

0 . 1 / 1 0 ( B J )

C244

2

0.1/10(BJ)

T I _ S D S

C 2 4 0 2

1 0 0 0 P ( B )

C 2 4 5 4

0 . 1 / 1 0 ( B J )

C 2 4 3 7

n o _ u s e

C243

8

0.1/10(BJ)

D I R _ B C K

C 2 4 6 7

0 . 1 / 1 0 ( B J )

R243

8

47X4

C242

3

0.1/10(BJ)

C 2 4 0 6

0 . 1 / 1 0 ( B J )

D G N D

T I _ S D S B

C 2 4 1 7

0 . 1 / 1 0 ( B J )

C 2 4 4 6

0 . 1 / 1 0 ( B J )

C 2 4 6 4

0 . 1 / 1 0 ( B J )

R 2 4 2 1

1 0 K

+ 3 . 3 D S P 1

R240

4

1M

L 2 4 0 1

B K P 1 0 0 5 H S 6 8 0 - T

A U P _ W C K

R 2 4 2 7

n o _ u s e

R243

5

47X

4

+ 3 . 3 D S P 1

C 2 4 3 0

n o _ u s e

T I _ S D C

R241

9

33

C 2 4 0 5

1 8 P ( C H )

C244

0

0.1/10(BJ

)

C2465

0.1/10(BJ)

D S P _ F M T

C 2 4 5 3

0 . 1 / 1 0 ( B J )

C242

9

0.1/10(BJ)

H D M I _ W C K / D L 2

R 2 4 1 2

3 3 X 4

R241

0

33X4

R241

1

33X4

C246

1

10/1

0

C246

2

10/1

0

C 2 4 6 9

1 0 / 1 0

R 2 4 2 9

4 . 7 K X 4

C 2 4 7 3

n o _ u s e

C242

0n

o_us

e

C247

5

no_us

e

C247

2n

o_us

e

C247

6

no_us

e

C 2 4 1 8

n o _ u s e

C 2 4 7 4

n o _ u s e

X L 2 4 1

2 0 M H Z

1

23

4

V D D

D Q 0

V D D Q

D Q 1

D Q 2

V S S Q

D Q 3

D Q 4

V D D Q

D Q 5

D Q 6

V S S Q

D Q 7

V D D

D Q M L

W E

C A S

R A S

C S

B A 0

B A 1

A 1 0

A 0

A 1

A 6

A 7

A 8

A 9

A 1 1

N C

C K E

C K

D Q M U

N C

V S S

D Q 8

V D D Q

D Q 9

D Q 1 0

V S S Q

D Q 1 1

D Q 1 2

V D D Q

D Q 1 3

D Q 1 4

V S S Q

D Q 1 5

V S S

A 2

V D D

V S S

A 5

A 3

A 4

+ 1 . 2 D S P

+ 1 . 2 D S P + 3 . 3 D

+ 3 . 3 D S P 1

C B 2 4 1

n o _ u s e

1

2

9

8

3

4

5

6

7

IC24

2

W25Q80DVSSIG

/C

S

D0

/W

P

GN

D

DI

CL

K

/HOL

D

VC

C

D I G I T A L 3 : D S P

I C / C B / X L : 2 4 1 -

O H T E R : 2 4 0 1 -

F L / F R

EMB_A[6]

EMA_OE

E M B _ D [ 1 1 ]

S B L / S B R

C V D D

GP2[6]

V e n d e r

EMB_RAS

UHPI_HRD

Y

CVD

D

E M B _ D [ 9 ] /

N C

Y E 0 0 5 B 0

EMB_A[10]

CVDD

CVDD

AXR0[2]

W 2 5 Q 8 0 D V S S I G

D V D D

EMB_A[4]

AXR0[0]

T C K

D V D D

AXR0[4]

A X R 1 [ 8 ]

E M B _ D [ 2 ]

AXR0[3]

T D I

C V D D

AHCLKX0

E M B _ D [ 3 ]

U S B 0 _ D P

C V D D

T R S T

U S B 0 _ V D D A 3 3

A X R 1 [ 3 ]

E M B _ D [ 4 ]

EMB_A[8]

AMUTE

1

D V D D

S e r i a l F l a s h M e m o r y

EMB_A[9]

E M B _ D [ 5 ]

E M B _ D [ 1 3 ]

O S C I N

E M B _ D [ 6 ]

E M B _ D [ 7 ]

6 4 M b i t

O S C O U T

EMB_A[0]

T M S

C V D D

A X R 1 [ 1 ]

DVDD

D G N D

Z E N T E L

N _ T R S T

E M B _ W E _ D Q M [ 0 ]

C V D D

T D O

D V D D

R S V 2

E M B _ W E _ D Q M [ 1 ]

DVDD

E M B _ W E

SPI0_SIMO[0]

U S B 0 _ V D D A 1 8

D V D D

SPI0_SOMI[0]

D V D D

DVDD

ACLKR

0

E M B _ C A S

EMB_A[5]

SPI1_CLK

AXR0[11]

A H C L K X 1

P L L 0 _ V D D A

C V D D

SPI1_SIMO[0]

DVD

D

E M A _ W E

SPI1_SOMI[0]

E M B _ D [ 1 4 ]

A C L K X 1

I C 2 4 3 a l t e r n a t e t h r e e p r o d u c t s b e l o w .

E M A _ D [ 7 ]

SPI0_ENA

D V D D

T D O

C V D D

D V D D

SPI0_CLK

P a r t T y p e

E M B _ D [ 1 5 ]

C V D D

EMB_A[7]

E M B _ D [ 1 0 ]

E M 6 3 8 1 6 5 T S D - 6 G

E M A _ D [ 6 ]

SPI0_SCS[0

]

AXR0[1]

EMB_CS[0]

EMB_BA[0]

E M B _ D [ 0 ]

E T R O N

to 001.sht(HDMI)

E M A _ D [ 5 ]

SPI1_SCS[0

]

E M B _ D [ 1 ]

P L L 0 _ V S S A

CVDD

Y D 7 6 2 B 0

P D ( + 3 . 3 V )

EMB_A[3]

AXR0[8]

D V D D

C V D D

SPI1_ENA

D V D D

( 8 M b i t s )

ACLKX

0

E M A _ D [ 4 ]

AXR1[11]

G P 7 [ 1 4 ]

E M A _ D [ 3 ]

AXR1[10]

CVDD

A X R 1 [ 4 ]

C V D D

AFSR

0

A 3 V 6 4 S 4 0 G T P - 6 0

D V D D

UART0_TX

D

D V D D

E N 2 5 Q 8 0 B - 1 0 4 H I P

S R L / S R R

B l a n k p r o d u c t o f I C 2 4 2 i s a a l t e r n a t e

o f t w o p r o d u c t s b e l o w .

U S B 0 _ D M

P a r t T y p e

E M A _ D [ 2 ]

UART0_RX

D

DVD

D

to 004.sht

(DIR & POWER)

E M A _ D [ 1 ]

AXR1[0

]

P a r t N o .

DVDD

EMA_D[0]

S E R I A L F L A S H B O O T

AFSX

0

CVD

D

EMA_A[12

]

U S B 0 _ V D D A 1 2

EMA_A[11

]

T C K

EMA_A[9]

A C L K R 1

AXR0[10]

EMA_A[8]

A F S X 1

DVD

D

EMB_A[12]

EMA_A[7]

EMB_A[11]

EMA_A[6]

E M B _ S D C K E

A X R 1 [ 6 ]

EMB_A[1]

EMA_A[5]

AXR0[5]

DVD

D

EMA_A[4]

E O N

R E S E T

CVD

D

Y D 4 8 7 C 0

A F S R 1

EMA_A[3]

EMA_A[2]

DVDD

EMA_A[1]

T M S

V e n d e r

AXR0[7]

EMA_A[0]

R T C _ X I

AXR0[6]

S D R A M

R T C _ C V D D

N C

AHCLKR0

EMA_A[10

]

W I N B O N D

E M B _ D [ 8 ]

Y F 5 8 7 A 0

EMB_A[2]

EMA_BA[1

]

A X R 1 [ 7 ]

C V D D

EMB_BA[1]

A X R 1 [ 5 ]

O S C V S S

DVD

D

E M B _ C L K

EMA_BA[0

]

P a r t N o .

C / S W

A X R 1 [ 2 ]

GP2[5]

E M B _ D [ 1 2 ]

T D I

AXR0[9]

DAC_FLT

to 004.sht(DIR & POWER)

to 002.sht(CPU)

W r i t t e n b y Y A M A H A : Y H 6 7 0 A 0

E S M T

X 9 6 2 5 C 0

M 1 2 L 6 4 1 6 4 A - 5 T G 2 Y

VDD

A3

A2

A1

A0

A10/AP

A12

A13

CS

RAS

CAS

WE

LDQM

VDD

VSSQ

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

VDDQ

VDDQ

VSSQ

DQ0

VDD

VSS

A4

A5

A6

A7

A8

A9

A11

NC

CKE

CLK

UDQM

NC

VSS

VDDQ

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

VSSQ

VSSQ

VDDQ

DQ15

VSS

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

IC243

: A3V64S40GTP

1M x 16-bit x 4 banks synchronous DRAM

CLK

CS

RAS

CAS

WE

C

ommand Decoder

C

ontr

ol Logic

Latch Cir

cuit

Input and Output

Buf

fe

r

Ro

w Decoder

Bank A

Sense Amplifier

Column Decoder

Data Control Circuit

L(U)DQM

DQ

CKE

Address

Clock

Generator

Row

Address

Buffer

Column

Address

Buffer

and

and

Refresh

Counter

Refresh

Counter

Mode

Register

Bank B

Bank C

Bank D

IC242

: W25Q80DVSSIG

8 M-bit flash memory with dual and quad SPI

Block Segmentation

xxFF00h

xxF000h

∙

xxFFFFh

xxF0FFh

∙

xx2F00h

xx2000h

∙

xx2FFFh

xx20FFh

∙

xx0F00h

xx0000h

∙

xx0FFFh

xx00FFh

Write Control

Logic

/WP(IO

2

)

∙

xx1F00h

xx1000h

∙

xx1FFFh

xx10FFh

∙

xxDF00h

xxD000h

Sector 15 (4KB)

Sector 14 (4KB)

Sector 13 (4KB)

Sector 2 (4KB)

Sector 1 (4KB)

Sector 0 (4KB)

∙

∙

∙

∙

xxDFFFh

xxD0FFh

∙

xxEF00h

xxE000h

∙

xxEFFFh

xxE0FFh

∙

0FFF00h

0F0000h

∙

0FFFFFh

h

F

F

0

3

0

0

h

0

0

0

3

0

0

h

F

F

0

2

0

0

h

0

0

0

2

0

0

h

F

F

0

1

0

0

h

0

0

0

1

0

0

h

F

F

0

0

0

0

h

0

0

0

0

0

0

0F00FFh

∙

Block 15 (64KB)

Security Register 3 - 0

∙

∙

∙

∙

∙

∙

08FF00h

080000h

∙

08FFFFh

0800FFh

∙

Block 8 (64KB)

07FF00h

070000h

∙

07FFFFh

0700FFh

∙

Block 7 (64KB)

00FF00h

000000h

∙

00FFFFh

0000FFh

∙

Block 0 (64KB)

Write Protect Logic and Row Decode

Status

Register

High Voltage

Generators

Page Address

Latch / Counter

Byte Address

Latch / Counter

Column Decode

And 256-Byte page Buffer

Beginning

Page Address

Data

Ending

Page Address

SPI

Command

and

Control Logic

/HOLD(IO

3

)

CLK

/CS

DI(IO

0

)

DO(IO

1

)

7

6

1

5

2

3

W25Q80BV

SDRAM 64 Mbit

No replacement part available.

RESISTOR

REMARKS

NO MARK

PARTS

NAME

CARBON

CARBON

METAL

METAL

METAL

FIRE

CEMENT

SEMI

FILM RESISTOR

FILM RESISTOR

OXIDE FILM RESISTOR

FILM RESISTOR

PLATE RESISTOR

PROOF CARBON FILM RESISTOR

MOLDED RESISTOR

VARIABLE RESISTOR

(P=5)

(P=10)

CHIP RESISTOR

REMARKS

CAPACITOR

PARTS NAME

NO

NO

MARK

MARK

ELECTROLYTIC

CAPACITOR

CERAMIC CAPACITOR

POLYESTER FILM CAPACITOR

POLYSTYRENE FILM CAPACITOR

MICA CAPACITOR

POLYPROPYLENE

FILM CAPACITOR

SEMICONDUCTIVE CERAMIC CAPACITOR

P

TANTALUM CAPACITOR

TUBULAR

S

CAPACITOR

CERAMIC

FILM

SULFIDE

POLYPHENYLENE

CAPACITOR

N O T I C E

U.S.A

G

CANADA

STANDARD

L

CHINA

AUSTRALIA

SINGAPORE

KOREA

GENERAL

U

C

T

A

K

R

JAPAN

(model)

B

BRITISH

J

SOUTH EUROPE

E

V

TAIWAN

F

RUSSIAN

P

LATIN AMERICA

S

BRAZIL

H

THAI

to DIGITAL 4/5

to DIGITAL 1/5

to DIGITAL 4/5

to DIGITAL 2/5

DIGITAL 3/5

★

All voltages are measured with a 10M

Ω

/V DC electronic voltmeter.

★

Components having special characteristics are marked

⚠

and must be replaced

with parts having specifications equal to those originally installed.

★

Schematic diagram is subject to change without notice.

●

電圧は、内部抵抗

10M

Ωの電圧計で測定したものです。

●

⚠印のある部品は、安全性確保部品を示しています。部品の交換が必要な場合、

パーツリストに記載されている部品を使用してください。

●

本回路図は標準回路図です。改良のため予告なく変更することがあります。

Details of colored lines

Red / full line:

Power supply (+)

Red /dashed line: Power supply (-)

Orange:

Signal detect

Yellow:

Clock

Green:

Protection detect

Brown:

Reset signal

Blue:

Panel key input

Summary of Contents for HTR-3069

Page 6: ...6 RX V381 HTR 3069 RX V381 HTR 3069 RX V381 K model RX V381 A model RX V381 B model ...

Page 7: ...7 RX V381 HTR 3069 RX V381 HTR 3069 RX V381 G F models RX V381 L model RX V381 S model ...

Page 8: ...8 RX V381 HTR 3069 RX V381 HTR 3069 RX V381 J model HTR 3069 U C models HTR 3069 T model ...

Page 9: ...9 RX V381 HTR 3069 RX V381 HTR 3069 HTR 3069 K model HTR 3069 B model TR 3069 G F models ...

Page 10: ...10 RX V381 HTR 3069 RX V381 HTR 3069 HTR 3069 L model ...

Page 138: ...RX V379 HTR 3068 ...