10

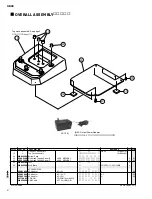

UB99

PIN

NO.

I/O

FUNCTION

NAME

PIN

NO.

I/O

FUNCTION

NAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

Vdd

Vss

XI

XO

Vdd5

/SYNCI

/SYNCO

Vdd5

CKI

CKO

CKSEL

Vss

MCKS

/SSYNC

/IC

/TEST

BTYP

/IRQ

TRIG

Vdd5

Vss

/CS

/WR

/RD

CA7

CA6

CA5

CA4

CA3

CA2

CA1

Vss

Vdd

CD15

CD14

CD13

CD12

CD11

CD10

CD09

CD08

CD07

CD06

Vss

Vdd

Vdd5

CD05

CD04

CD03

CD02

CD01

CD00

/WAIT

Vss

SI0

SI1

SI2

SI3

SI4

SI5

SI6

SI7

Vss

Vdd5

SO0

SO1

SO2

SO3

SO4

SO5

SO6

SO7

Vss

DB00

DB01

DB02

DB03

DB04

DB05

DB06

DB07

DB08

DB09

DB10

DB11

DB12

Vdd5

Vdd

I

O

I

O

I

O

I

I

I

I

I

I

O

I/O

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

I

I

I

I

I

I

I

I

O

O

O

O

O

O

O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Power supply (3.3 V)

Ground

System master clock input (60 MHz or 30 MHz)

System master clock output (High or 30 MHz)

Power supply (5 V)

Sync. signal input

Sync. signal output

Power supply (5 V)

System clock input (30 MHz)

System clock output (30 MHz)

System master clock select (0: 60 MHz, 1: 30 MHz)

Ground

Serial I/O master clock input (128 x Fs)

Serial I/O Sync. signal output

Initial clear (RESET)

Test mode setting (0: Test, 1: Normal)

Data bus type select (0: 8 bit, 1: 16 bit)

IRQ output

Trigger signal input/output

Power supply (5 V)

Ground

chip select signal input

Write signal input

Read signal input

Address bus of internal register

Ground

Power supply (3.3 V)

Data bus of internal register

Ground

Power supply (3.3 V)

Power supply (5 V)

Data bus of internal register

WAIT output

Ground

Serial data input

Ground

Power supply (5 V)

Serial data output

Ground

Parallel data bus

Power supply (5 V)

Power supply (3.3 V)

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

Vss

DB13

DB14

DB15

DB16

DB17

DB18

DB19

DB20

DB21

DB22

Vss

Vdd

DB23

DB24

DB25

DB26

DB27

DB28

DB29

DB30

DB31

TIMO/DBOB

Vss

Vdd5

DA00

DA01

DA02

DA03

DA04

DA05

DA06

DA07

Vss

DA08

DA09

DA10

DA11

DA12

DA13

DA14

DA15

Vss

Vdd

(n.c)

Vdd5

DA16

DA17

DA18

DA19

DA20

DA21

DA22

DA23

Vss

DA24

DA25

DA26

DA27

DA28

DA29

DA30

DA31

Vdd5

Vss

A00

A01

A02

A03

A04

A05

A06

A07

A08

A09

Vss

Vdd

A10

A11

A12

A13

A14

A15/RAS

A16/CAS

A17/CE

/WE

/OE

Vdd5

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

Ground

Parallel data bus

Ground

Power supply (3.3 V)

Parallel data bus

Timing signal output/ Parallel data bus output/ input

Ground

Power supply (5 V)

Memory data bus

Ground

Memory data bus

Ground

Power supply (3.3 V)

Not used

Power supply (5 V)

Memory data bus

Ground

Memory data bus

Power supply (5 V)

Ground

Memory address (SRAM, PSRAM, DRAM)

Ground

Power supply (3.3 V)

Memory address (SRAM, PSRAM, DRAM)

Memory address (SRAM, PSRAM)

Memory address (SRAM, PSRAM), /RAS (DRAM)

Memory address (SRAM, PSRAM), /CAS (DRAM)

Memory address (SRAM), /CE (PSRAM)

Memory write enable signal

Memory output enable signal

Power supply (5 V)

YSS910-S (XV988A00) DSP6 (Digital Signal Processor)