PSR-9000

17

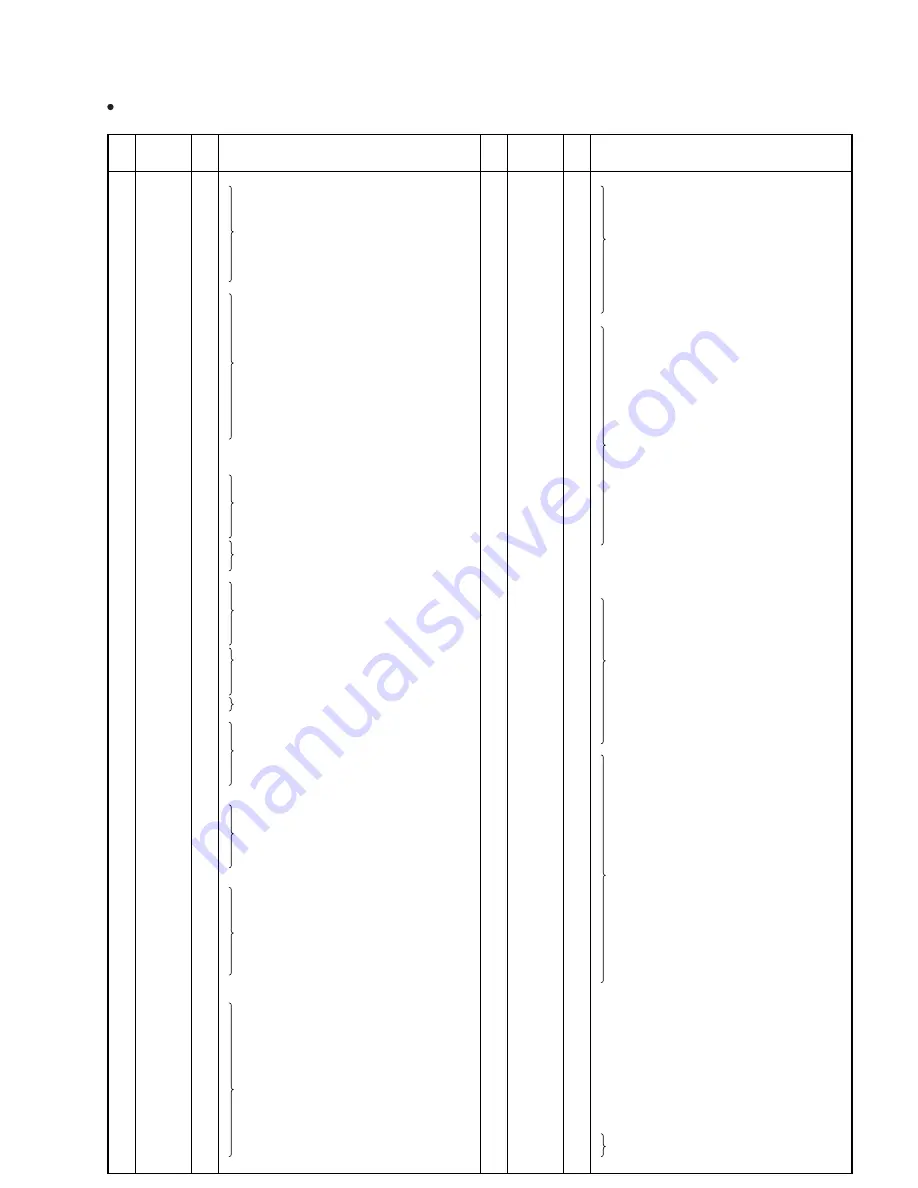

PIN

No.

NAME

I/O

FUNCTION

PIN

No.

NAME

I/O

FUNCTION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

Vss

CA0

CA1

CA2

CA3

CA4

CA5

CA6

CA7

CA8

CA9

CA10

CA11

VSS

CD0

CD1

CD2

CD3

CD4

CD5

CD6

CD7

CD8

CD9

CD10

CD11

CD12

CD13

CD14

VDD

VSS

CD15

CSN

WRN

RDN

VDD

SYSH0

SYSH1

SYSH2

SYSH3

SYSH4

SYSH5

SYSH6

SYSH7

KONO0

KONO1

KONO2

KONO3

VSS

SYSL0

SYSL1

SYSL2

SYSL3

SYSL4

SYSL5

SYSL6

SYSL7

KONI0

KONI1

VDD

VSS

KONI2

KONI3

DAC0

DAC1

WCLK

MELO0

MELO1

MELO2

MELO3

MELO4

MELO5

MELO6

MELO7

VDD

ADLR

MELI0

MELI1

MELI2

MELI3

MELI4

MELI5

MELI6

MELI7

VSS

RCASN

RA8

RA7

RA6

VDD

VSS

RA5

RA4

RA3

RA2

RA1

RA0

RRASN

RWEN

VSS

RD7

RD6

RD5

RD4

RD3

RD2

RD1

RD0

VSS

RD17

RD16

RD15

RD14

RD13

RD12

RD11

RD10

RD9

RD8

VDD

I

I

I

I

I

I

I

I

I

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

O

O

O

O

O

O

O

O

O

O

O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

I

I

O

O

O

O

O

O

O

O

O

O

O

O

I

I

I

I

I

I

I

I

O

O

O

O

O

O

O

O

O

O

O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

(Ground)

Address bus of internal register

(Ground)

Data bus of internal register

(Power supply)

(Ground)

Chip select

Write strobe

Read strobe

(Power supply)

NSYS/LNSYS upper 16 bits output

Key on data

(Ground)

NSYS input/LNSYS output lower 8 bits

Key on data input

(Power supply)

(Ground)

DAC output

DAC0/DAC1 word clock

MEL wave data output

(Power supply)

ADC word clock

MEL wave data input

(Ground)

DRAM column address strobe (RAS signal)

(Power supply)

(Ground)

DRAM address bus

DRAM row address strobe (RAS signal)

DARM write enable

(Ground)

(Ground)

DRAM data bus

(Power supply)

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

209

210

211

212

213

214

215

216

217

218

219

220

221

222

223

224

225

226

227

228

229

230

231

232

233

234

235

236

237

238

239

240

VSS

HMD0

HMD1

HMD2

HMD3

HMD4

HMD5

HMD6

HMD7

HMD8

HMD9

HMD10

HMD11

HMD12

HMD13

HMD14

HMD15

VSS

HMA0

HMA1

HMA2

HMA3

HMA4

HMA5

HMA6

HMA7

HMA8

HMA9

HMA10

VDD

VSS

HMA11

HMA12

HMA13

HMA14

HMA15

HMA16

HMA17

HMA18

HMA19

HMA20

HMA21

HMA22

HMA23

HMA24

VSS

MRASN

MCASN

MOEN

MWEN

VSS

LMD0

LMD1

LMD2

LMD3

LMD4

LMD5

LMD6

LMD7

VDD

VSS

LMD8

LMD9

LMD10

LMD11

LMD12

LMD13

LMD14

LMD15

VSS

LMA0

LMA1

LMA2

LMA3

LMA4

LMA5

LMA6

LMA7

LMA8

LMA9

LMA10

LMA11

VSS

LMA12

LMA13

LMA14

LMA15

LMA16

LMA17

VDD

VSS

LMA18

LMA19

LMA20

LMA21

LMA22

LMA23

LMA24

VSS

SYO

SYOD

QCLK

HCLK

CK256

SYSCLK

VDD

SYI

MCLKI

MCLKO

VDD

XIN

XOUT

VSS

ICN

CHIP2

SLAVE

TESTON

ACIN

DCTEST

VDD

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I

I

O

I

O

I

I

I

I

I

I

(Ground)

Wave memory data bus (Upper 16 bits)

(Ground)

(Power supply)

(Ground)

Wave memory address bus

(Ground)

RAS when DRAM(s) is connected to wave memory

CAS when DRAM(s) is connected to wave memory

Wave memory output enable

Wave memory write enable

(Ground)

Wave memory data bus (Lower 16 bits)

(Power supply)

(Ground)

(Ground)

(Ground)

Wave memory address bus (Lower data memory)

(Power supply)

(Ground)

(Ground)

Sync. signal for master clock

Sync. signal for HCLK/QCLK

1/12 master clock (64Fs)

1/6 master clock (128Fs)

1/3 master clock (256Fs)

1/2 master clock (384Fs)

(Power supply)

Sync. clock

Master clock input

Master clock output

(Power supply)

Crystal osc. input

Crystal osc. output

(Ground)

Initial clear

2 chips mode enable

Master/Slave select when 2 chips mode

Test pin

(Power supply)

TC203C760HF-002 (XS725A00)

SWP30B (AWM Tone Generator coped with MEG) Standard Wave Processor

TG: IC1