91

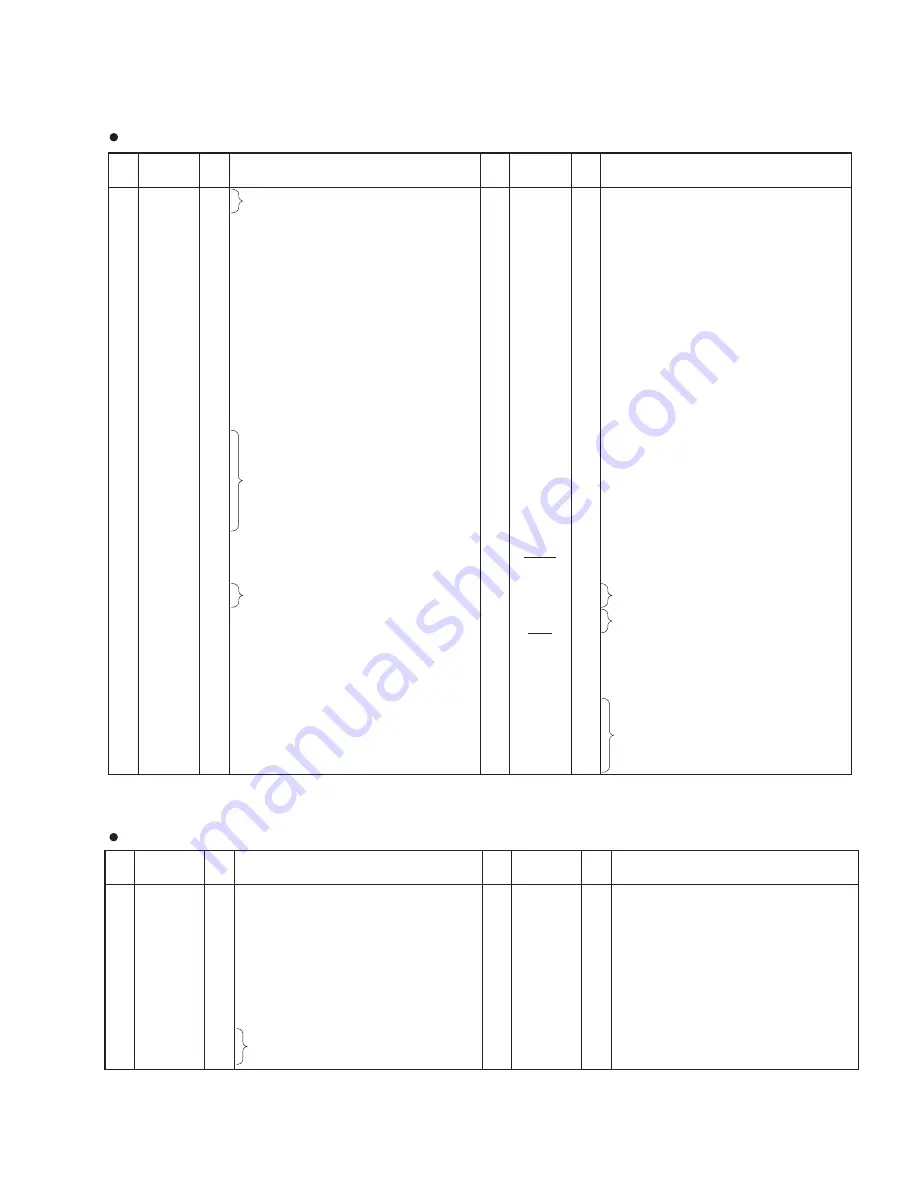

TF5/TF3/TF1

PIN

NO.

I/O

FUNCTION

NAME

PIN

NO.

I/O

FUNCTION

NAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

AIN2+

AIN2-

GND

VA

REF_GND

FILT+

VQ

GND

VA

GND

AIN4+

AIN4-

AIN3+

AIN3-

AIN7+

AIN7-

AIN8+

AIN8-

GND

VX

XTI

XTO

MCLK

I

I

I

I

I

O

O

I

I

I

I

I

I

I

I

I

I

I

I

I

I/O

I/O

I/O

Differential Analog– Audio signals are

presented differently to the delta sigma

modulators via the AIN+/- pins.

Ground– Ground reference. Must be

connected to analog ground.

Analog Power– Positive power supply for

the analog section

Reference Ground– For the internal sampling

circuits. Must be connected to analog ground.

Positive Voltage Reference– Reference

voltage for internal sampling circuits.

Quiescent Voltage– Filter connection for

the internal quiescent reference voltage.

Ground– Ground reference. Must be

connected to analog ground.

Analog Power– Positive power supply for

the analog section

Ground– Ground reference. Must be

connected to analog ground.

Differential Analog– Audio signals are

presented differently to the delta sigma

modulators via the AIN+/- pins.

Ground– Ground reference. Must be

connected to analog ground.

Crystal Oscillator Power– Also powers control

logic to enable or disable oscillator circuits.

Crystal Oscillator Connections– I/O pins

for an external crystal which may be used

to generate MCLK.

System Master Clock– When a crystal is

used, this pin acts as a buffered MCLK

Source (Output). When the oscillator function

is not used, this pin acts as an input for the

system master clock. In this case, the XTI

and XTO pins must be tied low.

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

LRCK/FS

SCLK

SDOUT4

SDOUT2

VLS

GND

SDOUT1

SDOUT3

GND

VD

CLKMODE

VLC

OVFL

DIF1

DIF0

M1

M0

RST

MDIV

AIN6+

AIN6-

AIN5+

AIN5-

AIN1+

AIN1-

I/O

I/O

O

O

I

I

O

O

I

I

I

I

O

I

I

I

I

I

I

I

I

I

I

I

I

Serial Audio Channel Clock– In I

2

S Mode,

Serial Audio Channel Select. When low, the

odd channels are selected.

In LJ Mode, Serial Audio Channel Select.

When high, the odd channels are selected.

In TDM Mode, a frame sync signal. When

high, it marks the beginning of a new frame

of serial audio samples. In Slave Mode, this

pin acts as an input pin.

Main timing clock for the Serial Audio Interface–

During Master Mode, this pin acts as an output,

and during Slave Mode it acts as an input pin.

Serial Audio Data– Channels 7,8.

Serial Audio Data– Channels 3,4.

Serial Audio Interface Power– Positive

power for the serial audio interface.

Ground– Ground reference. Must be

connected to analog ground.

Serial Audio Data– Channels 1,2.

Serial Audio Data– Channels 5,6.

Ground– Ground reference. Must be

connected to analog ground.

Digital Power– Positive power supply for

the digital section.

CLKMODE– Setting this pin HIGH places

a divide-by-1.5 circuit in the MCLK path to

the core device circuitry.

Control Port Interface Power– Positive

power for the control port interface.

Overflow– Detects an overflow condition

on both left and right channels.

DIF1, DIF0– Inputs of the audio interface

format.

Mode Selection– Determines the

operational mode of the device.

Reset– The device enters a low power

mode when low.

MCLK Divider– Setting this pin HIGH

places a divide-by-2 circuit in the MCLK

path to the core device circuitry.

Differential Analog– Audio signals are

presented differently to the delta sigma

modulators via the AIN+/- pins.

CS5368-CQZR

(X8488A00)

ADC

(Analog to Digital Converter)

HAAD (HACOM): IC903

PIN

NO.

I/O

FUNCTION

NAME

PIN

NO.

I/O

FUNCTION

NAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

DV

SS

DV

DD

MCLK

PDN

BICK

SDATA

LRCK

SMUTE/CSN

DFS0/CAD0

DEM0/CCLK

DEM1/CDTI

DIF0

DIF1

DIF2

-

-

I

I

I

I

I

I

I

I

I

I

I

I

Digital ground

Digital power 3.3 V

Master clock input

Power-down mode

Audio serial data clock

Audio serial data input

L/R clock

Soft mute/Chip select

Sampling speed mode select/Chip address 0

De-emphasis enable 0/Control data clock

De-emphasis enable 1/Control data input

Digital input format

15

16

17

18

19

20

21

22

23

24

25

26

27

28

TTL

VREFL

VREFH

AV

DD

AV

SS

AOUTR-

AOUTR+

AOUTL-

AOUTL+

VCOM

P/S

TST1/DZFL

TST2/CAD1

ACKS/DZFR

I

I

I

-

-

O

O

O

O

O

I

O

I

I/O

CMOS/TTL level select

Low level voltage reference input

High level voltage reference input

Analog power 5 V

Analog ground

Rch negative analog output

Rch positive analog output

Lch negative analog output

Lch positive analog output

Common voltage output

Parallel/serial select

Test 1/Lch zero input detect

Test 2/Chip address 1

Master clock auto setting mode/Rch zero input detect

AK4396VF-E2

(X8324A00)

DAC

(Digital to Analog Converter)

DA1 (DACOM): IC901

Summary of Contents for TF5

Page 10: ...10 TF5 TF3 TF1 866 716 225 599 225 599 TF5 TF3 Unit mm Unit mm DIMENSIONS...

Page 11: ...11 TF5 TF3 TF1 225 510 599 TF1 Unit mm...

Page 110: ...B B MAIN MAINCOM Circuit Board 2NA0 ZJ06330 3 110 TF5 TF3 TF1...

Page 111: ...B B Scale 90 100 Pattern side 2NA0 ZJ06330 3 111 TF5 TF3 TF1...

Page 113: ...WR 1 WR 1 DA2 Circuit Board Scale 90 100 Component side 2NA ZJ06430 2 113 TF5 TF3 TF1...

Page 116: ...WR 1 WR 1 7 WR 32 5 6 C C PS Circuit Board 2NA ZJ06320 2 116 TF5 TF3 TF1...

Page 119: ...Component side D D Component side 2NA ZJ06380 4 119 TF5 TF3 TF1...

Page 166: ...TF5 TF3 TF1 166 q w e r PLAY q PASS FAIL w CLOSE USER DEFINED KEYS B...

Page 202: ...TF5 TF3 TF1 202 7 SYSTEM SETUP ABOUT 8 HOME Initialize All Memory CANCEL OK OK EXIT...