YDP-131/YDP-131C

23

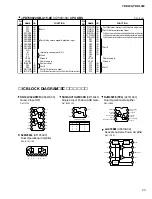

■

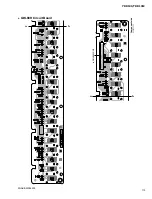

IC BLOCK DIAGRAM

(IC ブロック図)

PIN

NO.

I/O

FUNCTION

NAME

PIN

NO.

I/O

FUNCTION

NAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

P12

P11

P10

P47/KR7

P46/KR6

P45/KR5

P44/KR4

P43/KR3

P42/KR2

P41/KR1

P40/KR0

NC

IC

X2

X1

VSS0

VDD0

/RESET

P53

P52

P51/TO2

P50/TI0/TO0

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I/O

I/O

I/O

I/O

Port 1

Port 4/Key return signal detection input

Internally connected (N.C.)

Clock

Ground

Power supply

System reset

Port 5

Port 5/16-bit timer output

Port 5/External count clock input to 8-bit timer/8-bit timer output

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

P32/INTP2/CPT2

P31/INTP1

P30/INTP0

P22/RXD/SI0

P21/TXD/SO0

P20/ASCK//SCK0

P07

P06

P05

P04

P03

P02

P01

P00

NC

VDD1

VSS1

P17

P16

P15

P14

P13

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Port 3/External interrupt input/Capture edge input

Port 3/External interrupt input

Port 2/Asynchronous serial interface serial data input/Serial interface serial data input

Port 2/Asynchronous serial interface serial data output/Serial interface serial data output

Port 2/Asynchronous serial interface serial clock input/Serial interface serial clock

Port 0

Power supply

Ground

Port 1

µ

PD789022GB-A15-8E

(XZ560100) CPU KBS

SN74LV32APWR (X5647A00)

Quad 2 Input OR

1

2

3

1A

1Y

4

2A

5

2B

6

2Y

7

GND

1B

14

13

12

Vcc

4A

11

4Y

10

3B

9

3A

8

3Y

4B

SN74AHCT1G08DCKR (X0158A00)

Single 2-Input Positive-AND Gate

1

2

3

A

B

GND

5

4

Vcc

Y

INPUTS

FUNCTION TABLE

OUTPUT

A

B

Y

H

L

L

H

X

L

H

L

X

NJM4580L (XF195A00)

Dual Operational Amplifier

NJM4580E (TE2) (X2331A00)

Dual Operational Amplifier

1

2

3

4

-V

8

7

6

5

Output A

+V

Non-Inverting

Input A

-DC Voltage Supply

+DC Voltage

Supply

Output B

Inverting

Input B

Non-Inverting

Input B

Inverting

Input A

+

-

+

-

1

A

2

3

4

5

6

7

8

OUT

A

-IN

A

+IN

A

+IN

B

-IN

B

OUT

B

-V

+V

-

+

B

-

+

POWER

SWITCH

P/SW

IN 1

PRE GND

IN 2

REF

MT/SW

OUT 1

POWER GND

OUT 2

V

CC

BIAS

MUTE

CIRCUIT

Amp1

Amp2

LA4536M (X6813A00)

Headphone-stereo Power Amplifier

1

2

3

4

5

6

7

8

9

10