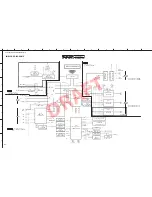

Pin

No.

Port Name

Function

Name

(P.C.B.)

I/O

Detail of Function

P

o

w

er On

Standb

y /

[Stb

y

A

W] / (iP

od)

Stb

y HDMI /

[Stb

y CEC]

When Appl

y

Cur

rent

1

PK6

DIR_SDO2

I

I

CDDA writing data input

PK6/AN14

2

PK7

TI_WARNG

I+

HiZ

DAMP error detect input

PK7/AN15

P.U to +3.3D

3

AVSS

AVSS

MCU

MCU

MCU

4

VREFH

VREFH

MCU

5

RESETn

N_RESET

MCU uCOM RESET input / Processed in microprocessor, usually pull-up

6

MODE

MODE

MCU Connected to GND / Processed in microprocessor, usually pull-up

7

SDA0 / PL0/

PWM_SDA

SIO

HiZ

PWM_MOD I2C data input/output

SDA0/TB0OUT

P.U to +3.3D

8

SCL0 / PL1/

PWM_SCL

SO

HiZ

PWM_MOD I2C data clock output

SCL0/TB1OUT

P.U to +3.3D

9

PL2

PWM_N_PDN

O

O

PWM_MOD power down output

PL2/SCK0/TB2OUT

10 INT0

TUNER_GPIO

IRQ

HiZ

TUNER GPIO input (INT pulse 1uS:RDS/SEEK detect)

PL3/INT0/TB3OUT

P.U to +3.3D

11 PL4

PWM_N_RST

O

O

PWM_MOD reset output

PL4/TXD1/TB4OUT

P.U to +3.3D

12 PL5

PWM_N_MUTE

O

O

PWM_MOD mute output

PL5/RXD1/TB5OUT

P.U to +3.3D

13 PL6

D4_N_WARNG

I+

HiZ

D4 protection / Processed in microprocessor, usually pull-up

PL6/SCLK1/TB6OUT/CTS1n

P.U to +3.3D

14 INT1

AC_PON_DET

IRQ

IRQ

AC Interrupt input to detect connection

PL7/INT1/TB7OUT

15 DVSS

DVSS

MCU

MCU

MCU

16 SCLK2

D4_SCK

SO

O

D4 synchronous clock

PM0/SCLK2/TB1IN0/CTS2n

17 TXD2

D4_MOSI

SO

O

D4 synchronous data output

PM1/TXD2/TB1IN1

18 RXD2

D4_MISO

SI

HiZ

D4 synchronous data input

PM2/RXD2/ALARMn

19 PM3

D4_N_CS

O

O

D4 chip select output

PM3/INT2

20 PM4

D4_N_RST

O

O

D4 reset output

PM4/SCLK3/CTS3n

21 PM5

D4_N_DISABLE

O

O

D4 PWM stop

PM5/TXD3

22 PM6

D4_PON

O

O

D4 power ON/OFF

PM6/RXD3

23 INT3

FLASH_RXD

IRQ

IRQ

FLASH_UART/232C (asynchronous communication) mode data input

PM7/INT3

(C1 interrupt) / Parallel input

24 TXD4

FLASH_TXD

SO

SO

FLASH_UART/232C (asynchronous communication) mode data output

PN0/TXD4

25 RXD4

FLASH_RXD

SI

SI

FLASH_UART/232C (asynchronous communication) mode data input

PN1/RXD4

Parallel input

26 PN2

232C_CTS

I

I

232C transmission enable input

PN2/SCLK4/TB2IN0/CTS4n

27 INT4

DIR_N_INT

IRQ

IRQ

DIR interrupt input

PN3/INT4/TB2IN1/RMIN0

28 TXD5

DSP_MOSI

SO

O

DSP/DIR synchronous data output

PN4/TXD5

29 RXD5

DSP_MISO

SI

HiZ

DSP/DIR synchronous data input

PN5/RXD5

30 SCLK5

DSP_SCK

SO

O

DSP/DIR synchronous clock

PN6/SCLK5/TBFIN0/CTS5n

31 INT8

DSP1_N_INT

IRQ

IRQ

DSP1 interrupt input

PN7/INT8/TBFIN1/RMIN1

32 PO0

D4_N_IRQ

I

HiZ

D4 IRQ input

PO0/TXD6/TB8OUT

33 PO1

DIR_N_CS

O

O

DIR chip select output

PO1/RXD6/TB9OUT

100

YSP-CU4300/YSP-CU3300/NS-WSW160

Y

SP-CU430

0/Y

SP-CU330

0/

NS-WSW1

60

DRAFT