YST-SW015

8

YST-SW015

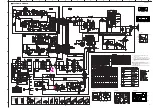

■

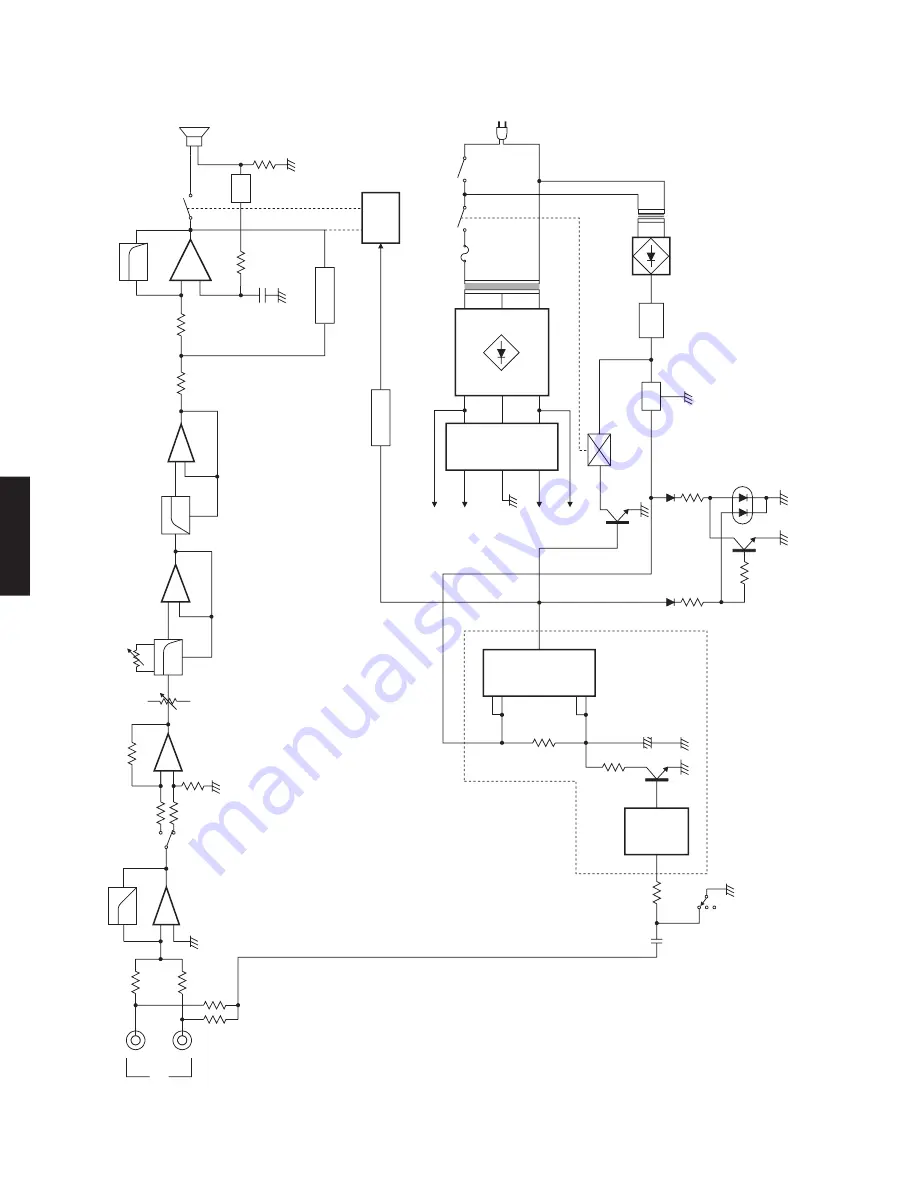

BLOCK DIAGRAM

LIMITER

IC3

REGULA

TOR

PO

WER SUPPL

Y

D1

SUB

PO

WER SUPPL

Y

D11

Q11

T1

T2

D13

D12

Q3

D9

+15

+B

-15

-B

Q9

Q10

RY

2

F1

PR

O

TECTION

0.1

DRIVER

RY

1

2

IC8

2

4

3

IC7B

IC7A

L.P

.F

12dB/oct

8

6

7

VR1

V

OLUME

VR2

HIGH CUT

7

6

5

IC1B

IC1A

1

2

3

MUSIC

SENSOR

IC4

TIMER

IC5

+

8

4

6

7

3

AU

T

O

ST

ANDBY

SW2

H

A

U

T

O

PO

WER ON/OFF CIRCUIT

Q5, 6, 7, 8

D4, 5, 22, 23

+

-

+

-

-

+

-

+

INPUT

L

R

Q12

R60

C46

PO

WER

AMP

1

H.P

.F

12dB/oct

OFF

L

IC9

REGULA

T

O

R

Q4, 13

D14

REGULA

T

O

R

(R,

T

, K models only)

PO

WER

SW5

A.N.I.C

IC2, Q16

L.P

.F

6dB/oct

1

10

L.P

.F

6dB/oct

PHASE

REVERSE

NORMAL

Q14, 15