3-50

3-51

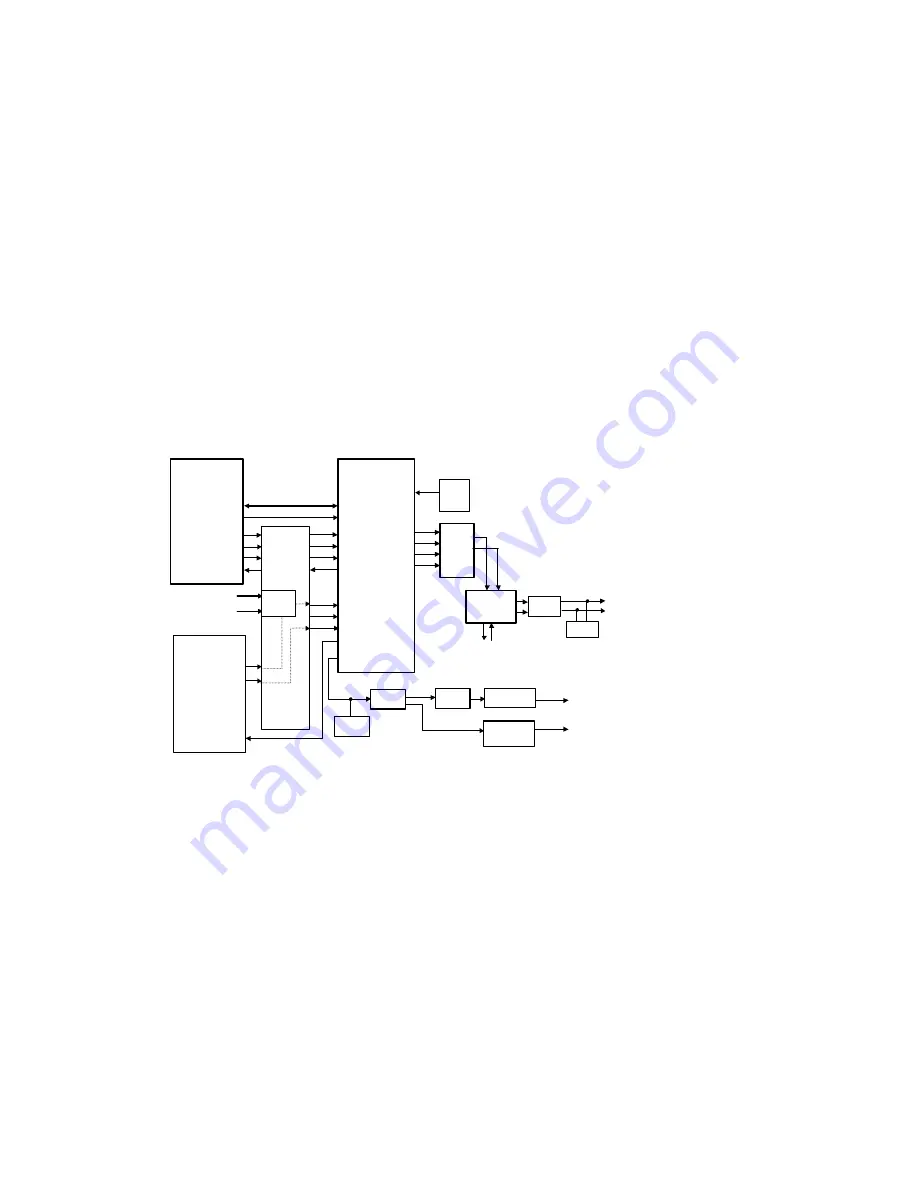

PPC405GP

CPU

HD-1

Per_Data[0:7]

STi4600

AC -3 Decoder

27MHz

HD-1

PLL

Per_Addr[0:7]

/CS6

PER_RW

/PER_OE

/RQ4

System

CPLD

PES0_DATA

PES0_STROBE

/CS

/WR

/RD

REQ

SIN

LRCLKIN

STR

MCLK

SCLK

LRCLK

PCM_OUT0

Address

Data

PES0_REQ

REQ

IE958_OUT

SPDIF Out

RCA Jack

PCMCLK

Per_Data[0:7]

Per_Addr[0:4]

Per_Addr[20:23]

DS8921

422 Driver

35101

Trans

CS4340

Audio

DAC

TDA7440D

Volume

Controller

MC33078

OP AMP

Variable(or fixed) Audio

L/R Out

I2C Bus_B

74LCX157

Mux

Audio

Mute

STOREHOUSE

OUTPUT

Connector

SPDIF Out

STOREHOUSE OUTPUT Jack

Audio

Mute

Address

Data

Decoder

6) AUDIO BLOCK DIAGRAM

Summary of Contents for HDR230

Page 28: ......

Page 34: ......

Page 37: ......

Page 38: ...3 17 3 18 4 WAVEFORMS 1 DIGITAL SYSTEM CLOCK GENERATOR PART 1 2 3...

Page 39: ...3 19 3 20 2 DIGITAL SYSTEM SYSTEM MEMORY PART 1 2 3...

Page 40: ...3 21 3 22 3 VIDEO PLL PART 1 2...

Page 41: ...3 23 3 24 4 VIDEO OUTPUT CONNECTOR PART 1 2 3 BMK800 BMK800 BMK800 33PF 33PF 33PF...

Page 43: ...3 27 3 28 6 PVR CLOCK PART 1 2 3...

Page 44: ...3 29 3 30 7 VSB VSB DECODER PART 1...

Page 45: ...3 31 3 32 8 VSB DOWN CONVERTER PART 1...

Page 46: ...3 33 3 34 9 MICOM DOWN CONVERTER PART 1...

Page 47: ......

Page 65: ...3 74 3 75 10 VSB CIRCUIT DIAGRAM IF VSB TP Data clock error valid 03 3 15 HDR230 DNS...

Page 67: ...3 78 3 79 12 POWER IF COM VIDEO CIRCUIT DIAGRAM CVBS OUT Y OUT C OUT 03 3 15 HDR230...

Page 68: ...3 80 3 81 13 FRONT CIRCUIT DIAGRAM RIGHT LEFT 03 3 15 HDR230...

Page 69: ...3 82 3 83 8 PRINTED CIRCUIT DIAGRAMS 1 DIGITAL MAIN PRINTED CIRCUIT DIAGRAMS TOP...

Page 70: ...3 84 3 85 2 DIGITAL MAIN PRINTED CIRCUIT DIAGRAMS BOTTOM...

Page 72: ...3 88 3 89 5 POWER PRINTED CIRCUIT DIAGRAM LOCATION GUIDDE...