Copyright

©

Cirrus Logic, Inc. 2007

(All Rights Reserved)

Preliminary Product Information

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

30 W Digital Audio Amplifier with Integrated ADC

Digital Amplifier Features

Fully Integrated Power MOSFETs

No Heatsink Required

–

Programmable Power Foldback on

Thermal Warning

–

High Efficiency

> 100 dB Dynamic Range

< 0.1% THD+N @ 1 W

Configurable Outputs (10% THD+N)

–

1 x 30 W into 4

Ω,

Parallel Full-Bridge

–

2 x 15 W into 8

Ω

, Full-Bridge

–

2 x 7 W into 4

Ω

, Half- 1 x 15 W

into 8

Ω

, Full-Bridge

Built-In Protection with Error Reporting

–

Overcurrent/Undervoltage/Thermal

Overload Shutdown

–

Thermal Warning Reporting

PWM Popguard

®

for Half-Bridge Mode

Click-Free Start-Up

Programmable Channel Delay for System

Noise & Radiated Emissions Management

ADC Features

Stereo, 24-bit, 48 kHz Conversion

Multi-bit Architecture

95 dB Dynamic Range (A-wtd)

-86 dB THD+N

Supports 2 Vrms Input with Passive

Components

System Features

Asynchronous 2-Channel Digital Serial Port

32 kHz to 96 kHz Input Sample Rates

Operation with On-Chip Oscillator Driver or

Applied SYS_CLK at 18.432, 24.576 or

27.000 MHz

Integrated Sample Rate Converter (SRC)

–

Eliminates Clock-Jitter Effects

–

Input Sample Rate Independent Operation

–

Simplifies System Integration

Spread Spectrum PWM Modulation

–

Reduces EMI Radiated Energy

Low Quiescent Current

(Features continued on

)

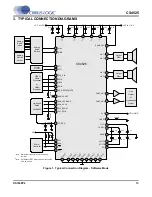

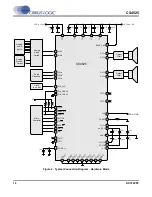

VP

Amplifier

Out 1

Amplifier

Out 2

PGND

Amplifier

Out 3

Amplifier

Out 4

Stereo

Analog In

PWM Modulator

Output 2

PWM Modulator

Output 1

Gate

Drive

Gate

Drive

Gate

Drive

Gate

Drive

Multi-bit

ΔΣ

Modulator

with

Integrated

Sample Rate

Converter

Audio

Processing

Parametric EQ

High-Pass

Bass/Treble

Adaptive

2-Ch Mixer

2.1 Bass Mgr

Linkwitz-Riley

Crossover

De-Emphasis

Serial Audio

Clocks & Data

Serial Audio

Data I/O

Serial Audio

Clocks & Data

Serial Audio Input Port

Multi-bit

ΔΣ

ADC

Volume

Crystal Driver

I/O

System Clock

Crystal Oscillator Driver

Register /Hardware

Configuration

I²C or Hardware

Configuration

Reset

Interrupt

Error Protection

Thermal Warning

Over Current

Thermal Feedback

Under Voltage

HP Detect/Mute

PWM

2.5 V to 5 V

8 V to 18 V

Auxiliary Serial Port

Serial Audio

Delay Interface

Loudness

Compensation

NOVEMBER '07

DS726PP2

CS4525