Reviews:

No comments

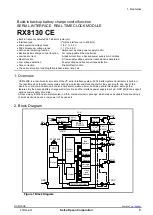

Related manuals for RX8130CE

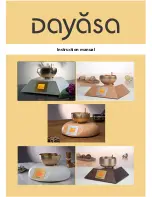

6945

Brand: Dayasa Pages: 12

RCR-22

Brand: Sangean Pages: 1

RCR-8WF

Brand: Sangean Pages: 201

t226

Brand: Timex Pages: 8

RAC-001

Brand: Life Pages: 4

DQ-746

Brand: Casio Pages: 2

88202

Brand: SkyScan Pages: 5

KH 2201

Brand: Kompernass Pages: 50

31310T

Brand: SkyScan Pages: 7

WT-8005U-S

Brand: La Crosse Technology Pages: 8

404-3229

Brand: La Crosse Technology Pages: 2

home LTCP 01

Brand: Somogyi Pages: 11

90446742

Brand: IKEA Pages: 12

Spider-Man TimeProjector RP160SP

Brand: LEXIBOOK Pages: 1

DR900

Brand: LEXIBOOK Pages: 24

BT-1308

Brand: SOUNDMASTER Pages: 10

MS115BT

Brand: ACOUSTIC SOLUTIONS Pages: 28

616-1410B

Brand: La Crosse Technology Pages: 10